今天和大侠简单聊一聊FPGA设计中不同设计方法硬件资源消耗对比,话不多说,上货。

在这里,我们使用Verilog HDL 设计计数器,通过两种不同的写法,对比资源消耗。计数器实现的功能是计数记到24,清零,然后重新计数。很简单的两个例子,让我们来看一看。

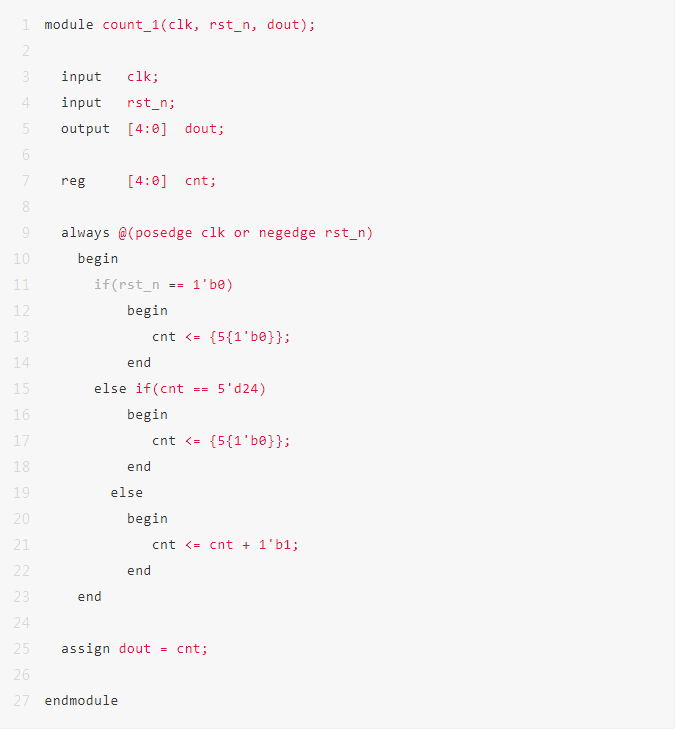

第一种设计方法,代码如下:

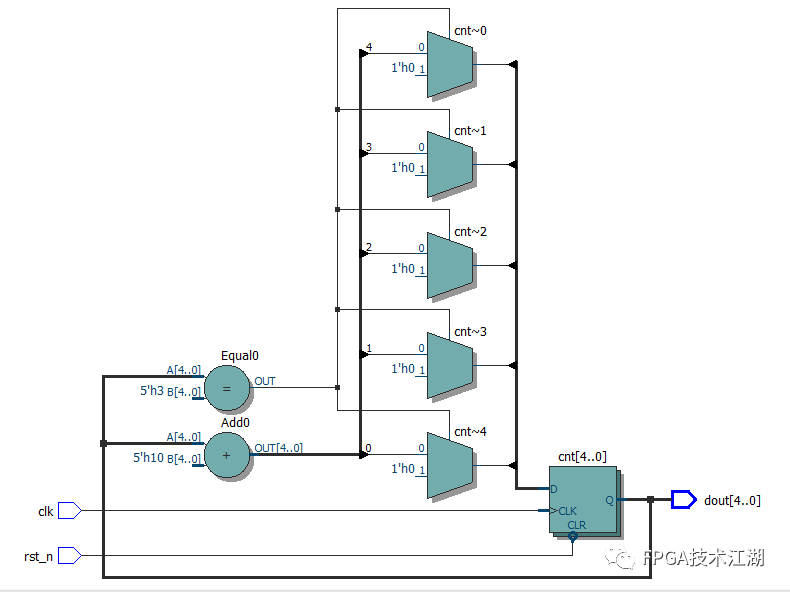

RTL级视图如下:

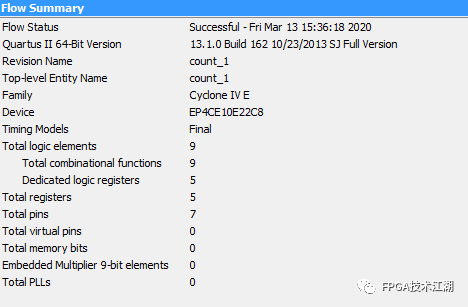

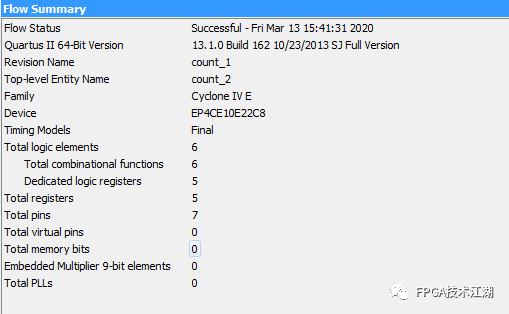

现在来看看消耗的逻辑单元。如下:

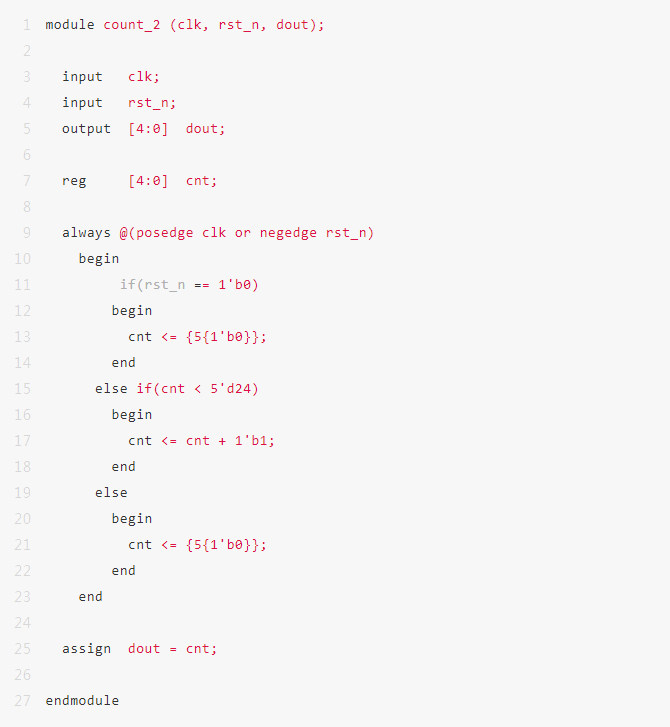

第二种设计方法,代码如下:

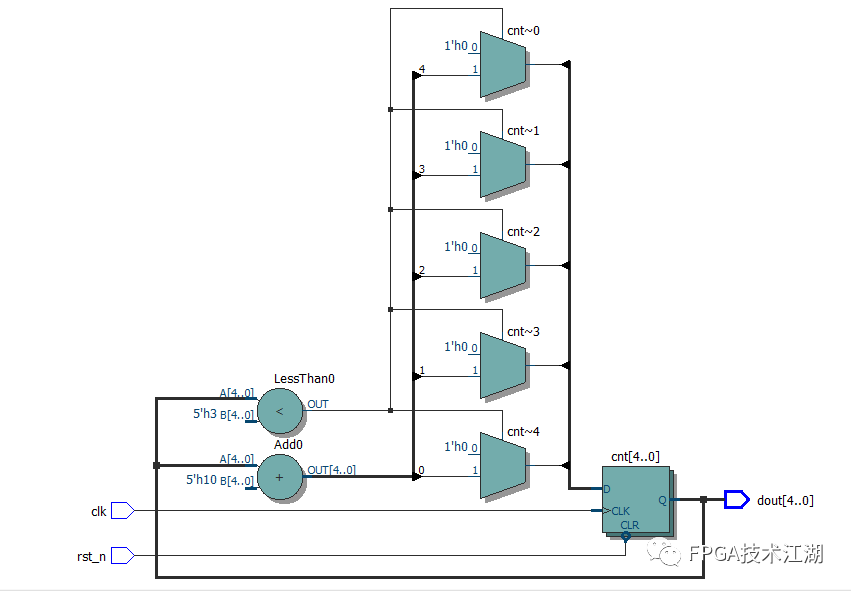

RTL级视图如下:

RTL级视图如下:

第一种写法比第二种写法多耗了3个逻辑单元。

从上面的逻辑单元和RTL级视图对比,在用计数器实现相同的功能时,可以看出 == count 消耗的逻辑单元比 < count消耗的逻辑单元要多。所以我们在做设计的时候需要考虑到硬件资源的时候也需要优化自己的设计代码,在做时序约束分析的时候也是一样的道理,后续再更新相关内容,告辞。

我要赚赏金

我要赚赏金