大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,TLC5620驱动教程。话不多说,上货。

TLC5620驱动教程

在FPGA处理完数字信号之后,我们有些情况下是需要将数字信号转变为模拟信号再输出的。比如音频信号在滤波后,需要转换为声音信号进行输出。此次,我们要讲数字信号转换为电压信号进行输出,以便我们后续可以用示波器之类的器械观察信号。

我们采用的芯片为TLC5620,是一款8bit四通道的数模转换器。

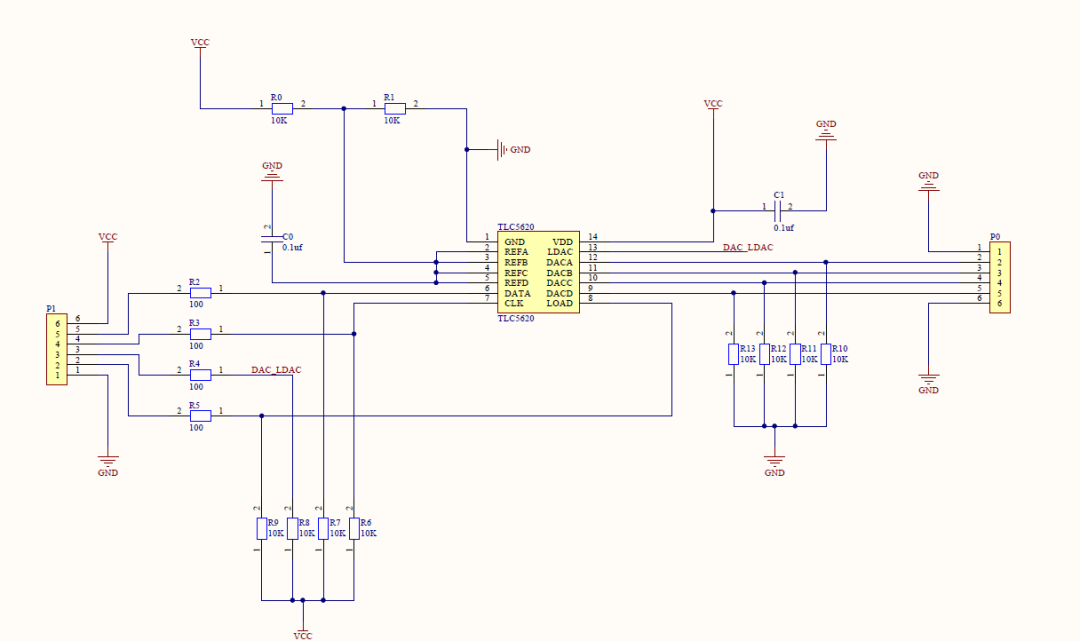

在四路通道中,我们可以设置4种不同的参考电压进行转换使用。但是在此次实验中,我们采用的四路参考电压一样,如下图:

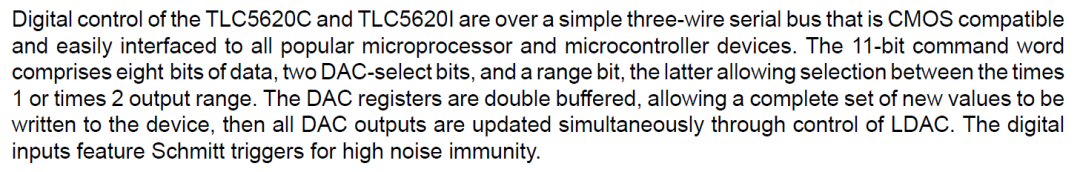

接下来我们介绍一下此芯片的一些特征以及手册对芯片的描述。下图为官方手册对芯片的一段描述:

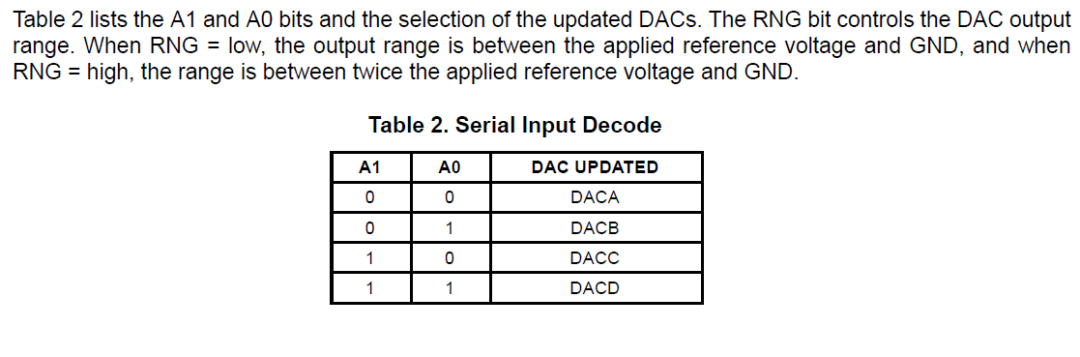

TLC5620是一款使用3线串行总线控制的芯片。11bit的命令中包含8bit数据、2bit通道选择、1bit输出范围选择bit。输出范围选择,可以输出一倍或者两倍的参考电压差值范围。当两级锁存器都打开时,新的数据可以进入到芯片。下图为芯片的框图:

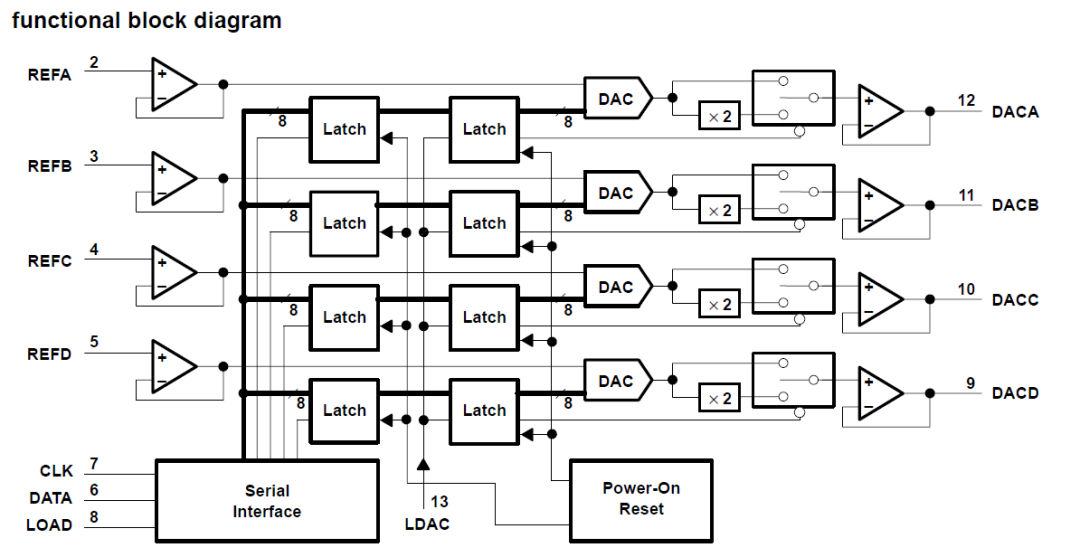

端口介绍:

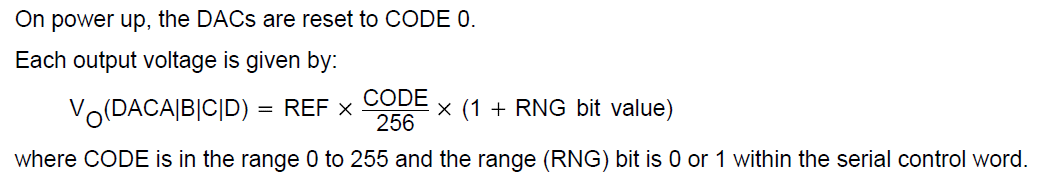

我们的数据为8bit,那也就是将电压范围划分为256份,我们的数字信号会对应成电压进行输出,所以我们的输出电压的计算公式为:

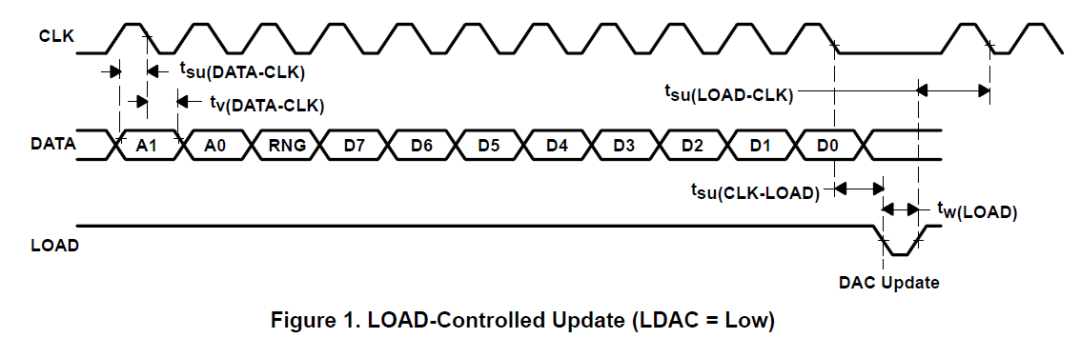

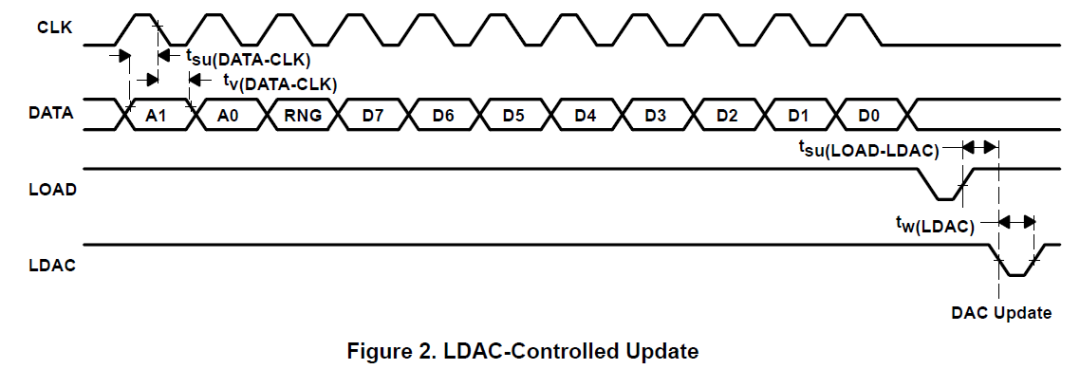

接下来我们看一下时序图:

当LOAD为高电平时,数据被锁存进DATA在每一个时钟下降沿,一旦数据所有的bit被采集到,LOAD被拉低,将寄存器中的数据传输到被选择的DAC中。如图一所示,当LDAC为低电平时,LOAD信号拉低,被选择的DAC芯片输出电压会更新。如果LDAC为高电平,电压更新将会被禁止,直到我们将LDAC拉低,如图二:

对于我们的通道选择,如下图:

当RNG=0时,输出电压为一倍范围,当RNG=1时,输出电压为两倍范围。

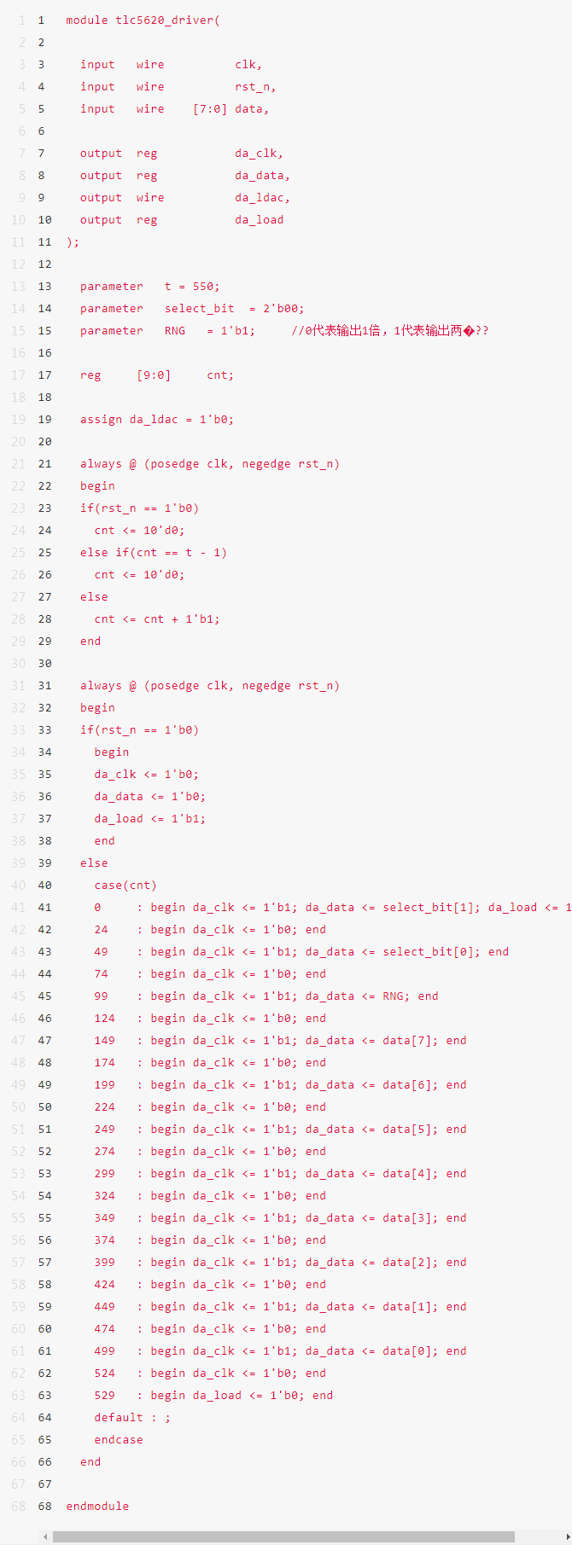

接下来,我们来做一下芯片的驱动,同样可以使用线性序列机。转换总周期为11us的时间。

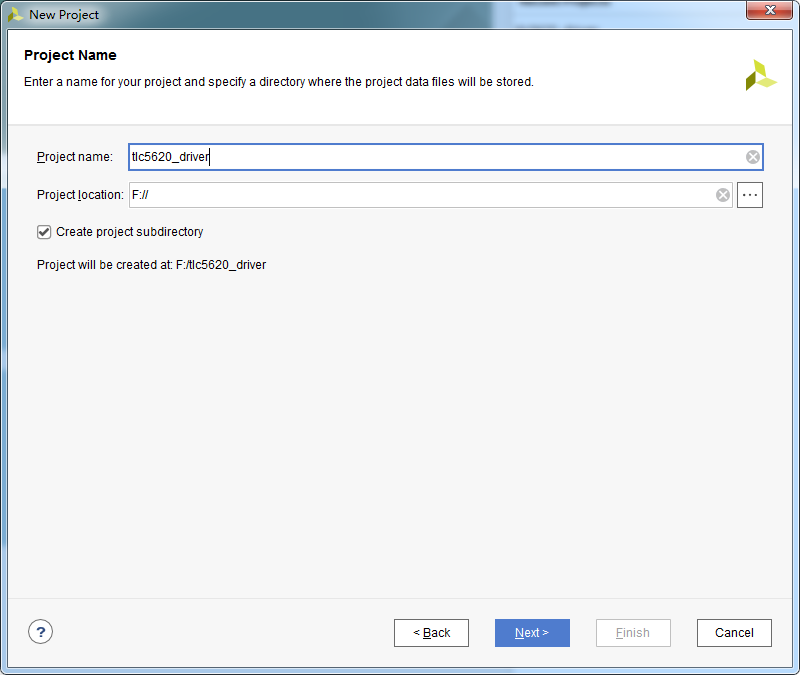

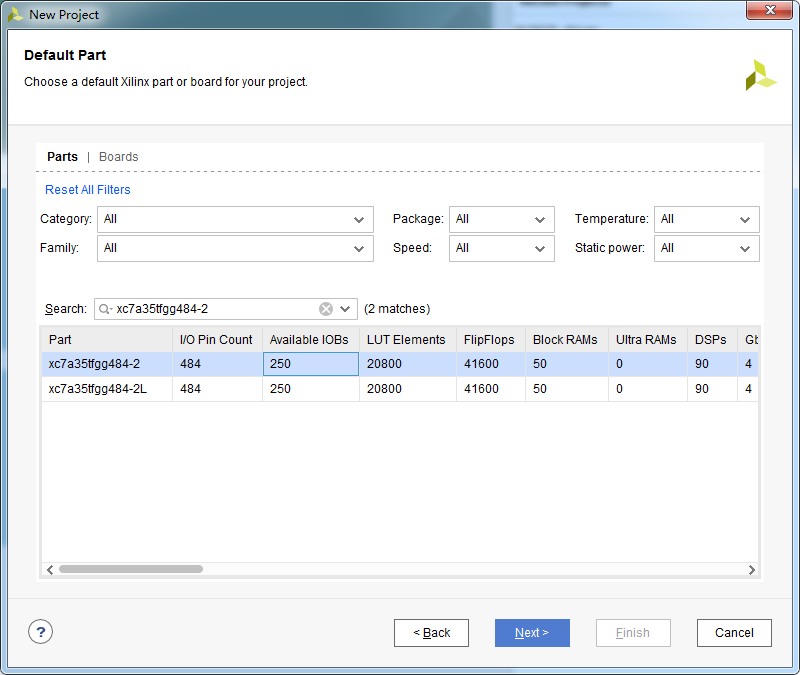

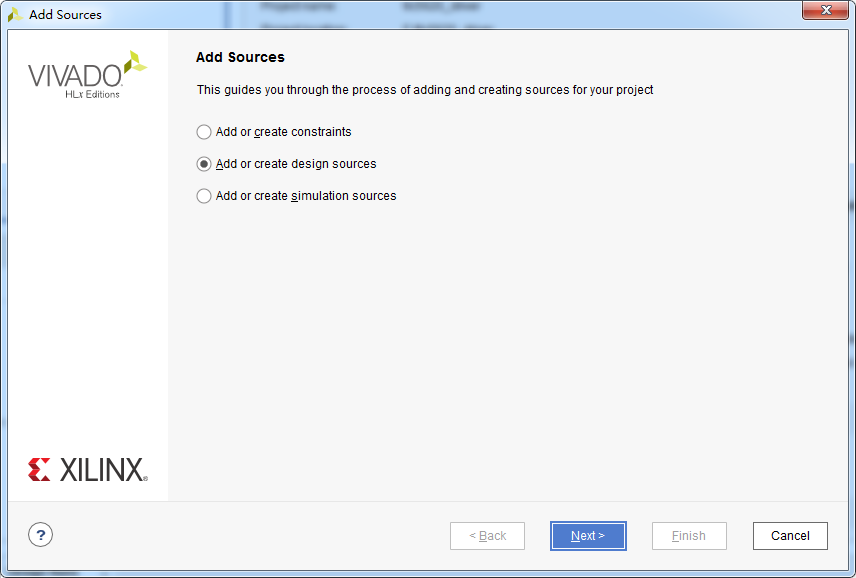

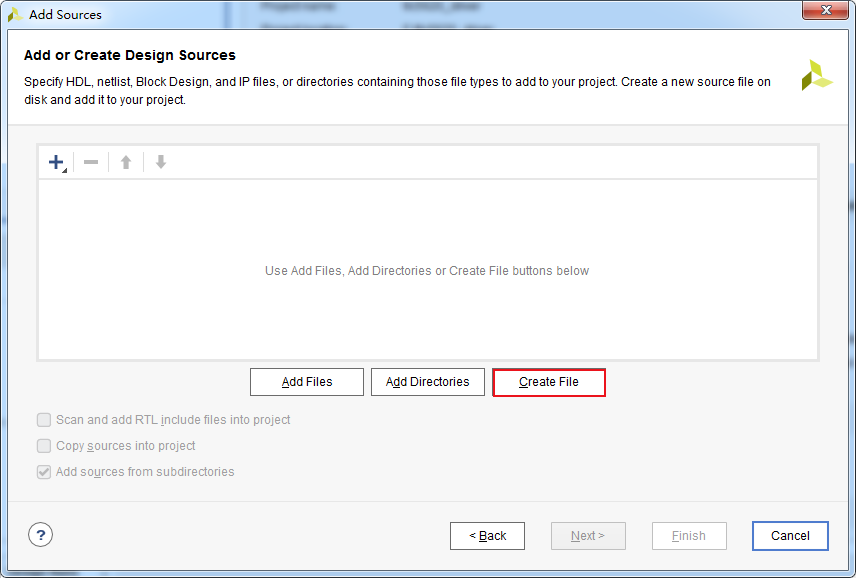

首先我们先新建工程。

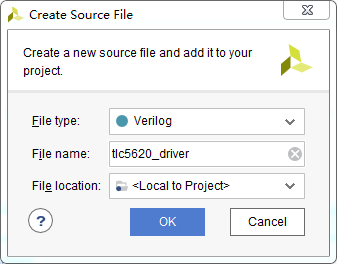

新建代码文件,写入代码:

驱动代码如下:

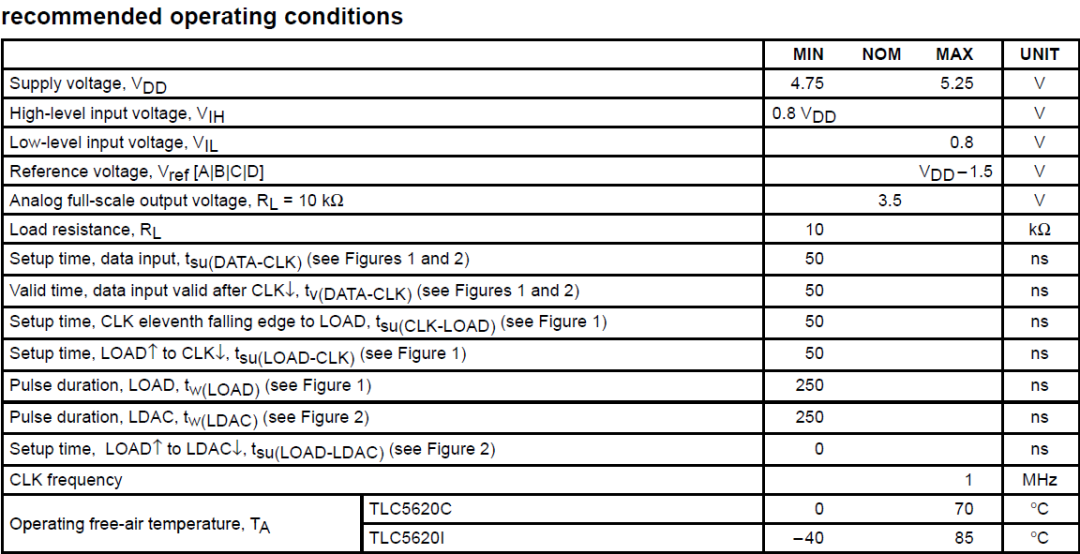

在写驱动代码时,我们需要注意时序图中的一些时间要求,比如,数字信号的建立时间和保持时间,以及load信号的建立时间与保持时间。时间要求如下图:

由上图可以得出结论,芯片的驱动时钟最大为1MHz。数据的建立时间与保持时间最小值都为50ns。如果我们在时钟上升沿发送数据,那么我们发送的数据,建立时间与保持时间最小值为500ns。满足条件。

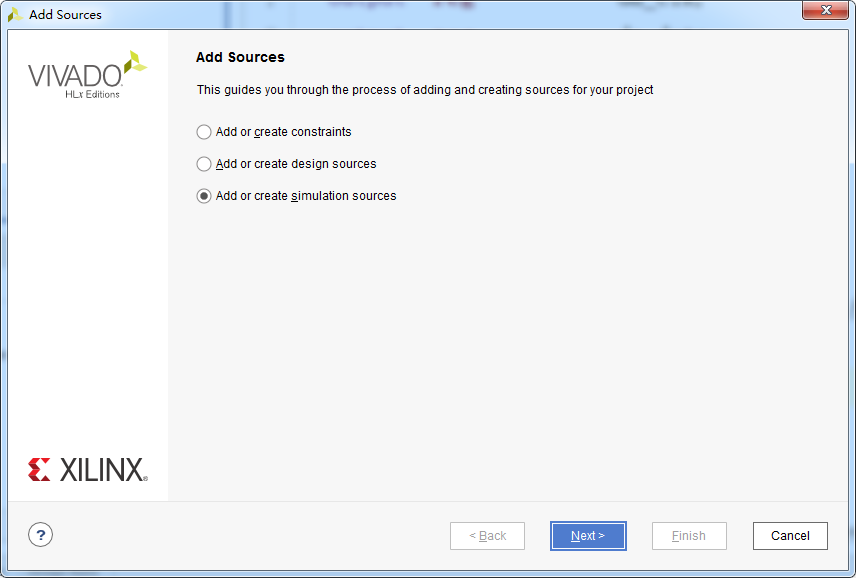

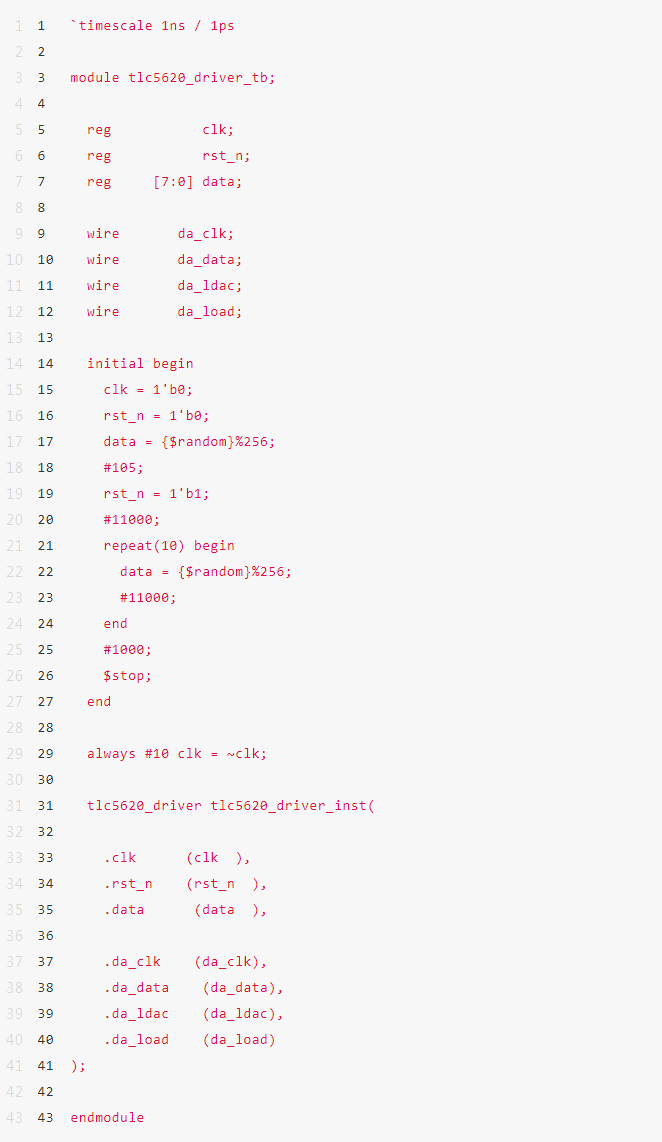

接下来我们写一下仿真看一下波形。

代码如下:

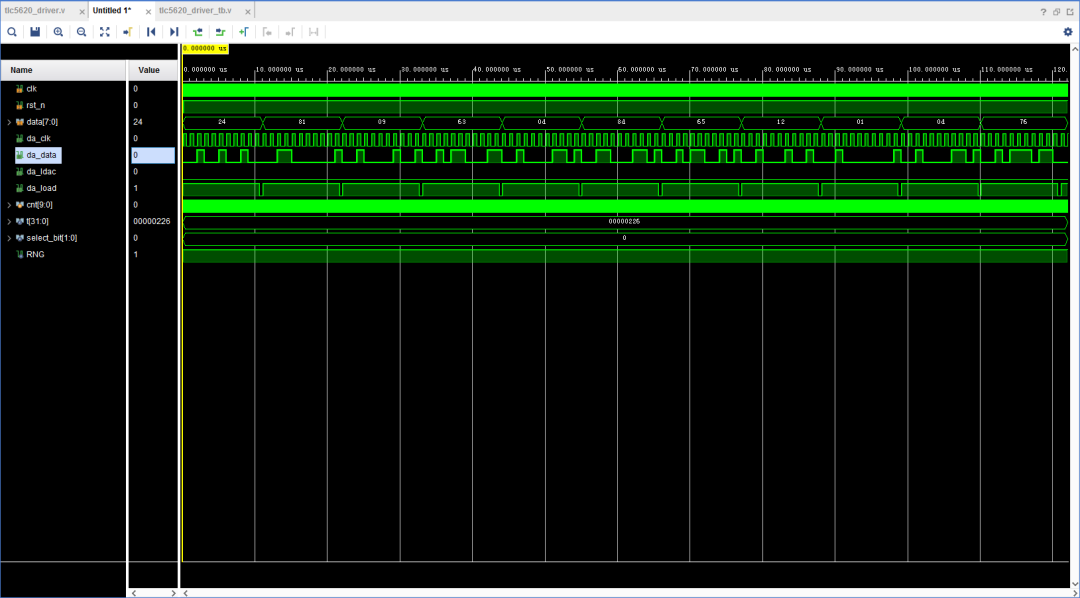

运行波形,观察仿真波形:

观察da_clk、da_data、da_load、da_ldac波形全部正常,即说明驱动正确。

我要赚赏金

我要赚赏金