我想做以下事情:

1。通过 SPI 向 SD 卡发送 6 字节命令,在 TX Empty 上中断(当命令完全移出 FIFO 时)

2。在 ISR 中,使用 scb_spiuartClearrxBuffer () 或读取字节来清空接收 FIFO。

3。发送虚拟字节 0xFF,在 TX 空时中断,读取 RX 字节,直到收到非 0xFF 值(来自 SD 卡的响应)。

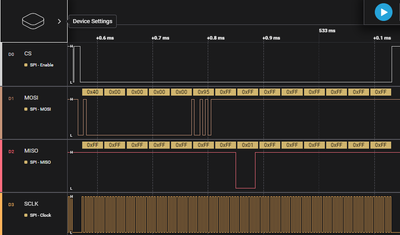

因此,假设 SD 卡对命令之后的第二个虚拟字节作出响应,我应该看到命令之后总共传输了 3 个虚拟字节。 但是,我却在代码和逻辑分析器跟踪中看到了 8:

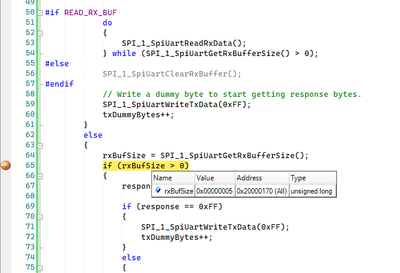

使用调试器,我将问题范围缩小到了 ISR 中的这一部分:

遇到该断点时的总线跟踪(由于调试器暂停,SCB 会自动取消对 CS 的断言):

上面的步骤 2 是第 51-54 行,其余的就是步骤 3。 尽管我已经从 RX 缓冲区读取了所有字节,或者使用了 clearRxBuffer (),但在传输另一个字节之后,RX 缓冲区大小读取 5,尽管之前打破 do/while 循环时为 0!

为什么?如果我从 FIFO/Buffer 中读取所有 RX 字节,然后再传输一个字节,为什么接收缓冲区中还有 5 个字节? 这 5 个加上 3 个虚拟字节 = 在从 FIFO 读取响应字节之前传输的 8 个额外字节。

我认为这个问题可能是由于我向 TX 缓冲区写入 0xFF 后直接触发 TX Empty 中断所致,因为当最后一个 FIFO 元素从 FIFO

移到移位器时,空就会触发。 例如,也许空中断会触发不止一次? 有没有更好的方法来进行单字节传输/检查响应,而无需SCB自动取消对CS的断言(即

没有 SPI_DONE 中断)?

我已经附上了这个项目,它以 CY8CKIT046 为目标,SD 模块通过 PMOD 接头(端口 6)连接到 SCB。

共2条

1/1 1 跳转至页

SPIMasterRX如何在保持CS低位的情况下从从机接收可变字节数?

关键词: SPI SD卡 CS

2楼

SPI Master RX的工作原理是主机通过SPI总线发送数据给从机,并且可以通过从机传输回来的数据接收到主机。在保持CS低位的情况下,SPI主机可以接收可变字节数的数据。

你已经完成了发送命令和接收从机响应的代码。你期望只接收3个虚拟字节,但实际上接收了8个字节。

这个问题可能是由于数据的传输速度过快导致的。当实际传输的数据长度小于预期时,原因可能是以下几点:

1. 主机在接收到最后一个字节之前停止接收数据。这可能是由于主机设备读取数据的速度比从机设备发送数据的速度快。

2. 从机没有及时停止数据传输。这可能导致数据在从机中缓冲,并继续发送到主机,直到缓冲区满为止。

为了解决这个问题,你可以尝试以下几个方法:

1. 增加适当的延时,以便主机设备有足够的时间来接收数据。可以通过延长CS低位的时间或在发送命令之后增加适当的延时来实现。

2. 在接收到预期数量的字节后,主动停止从机发送数据。可以在接收到预期数量的字节后,通过设置SPI控制器的控制寄存器来停止数据传输。

3. 检查使用的硬件和软件配置是否正确。确保SPI主机和从机的时钟和模式设置正确。

共2条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |