code.pdf

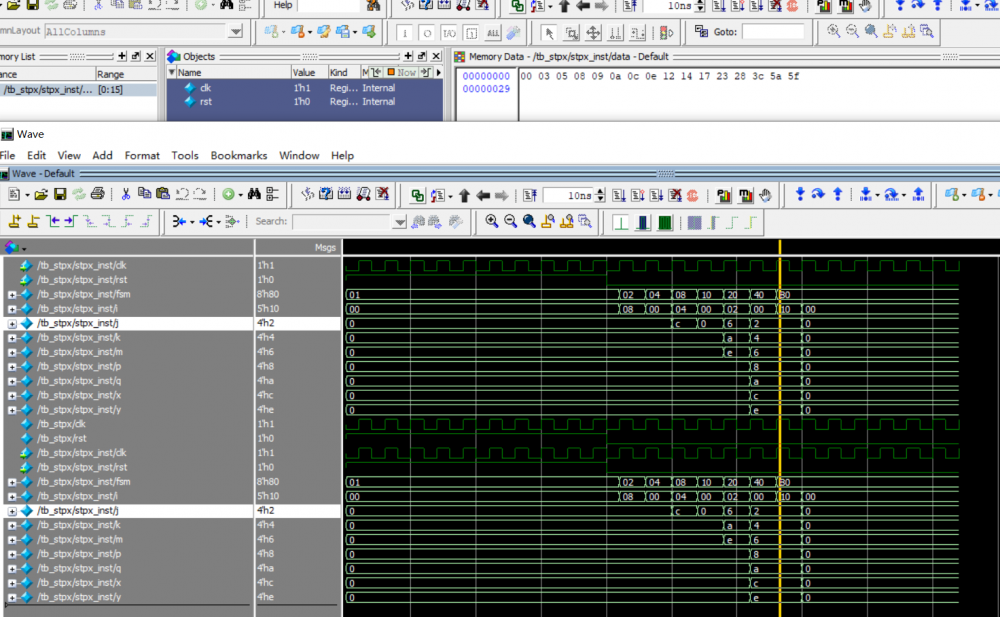

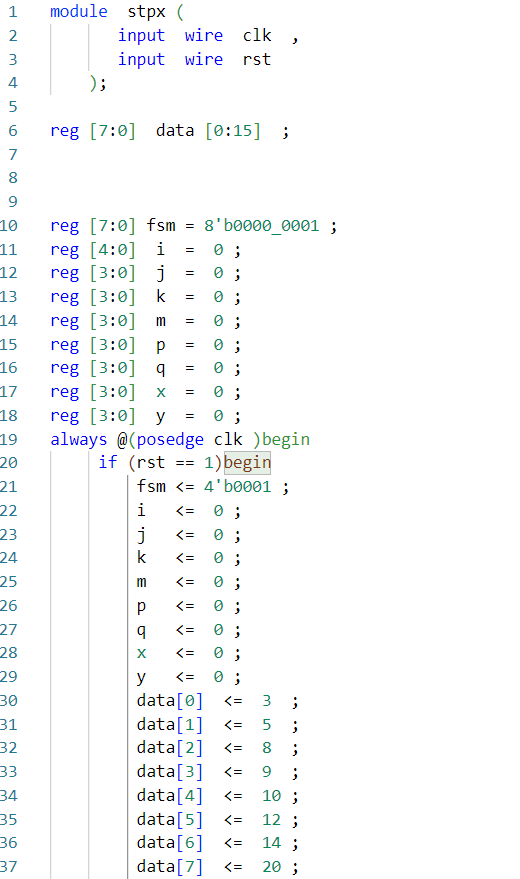

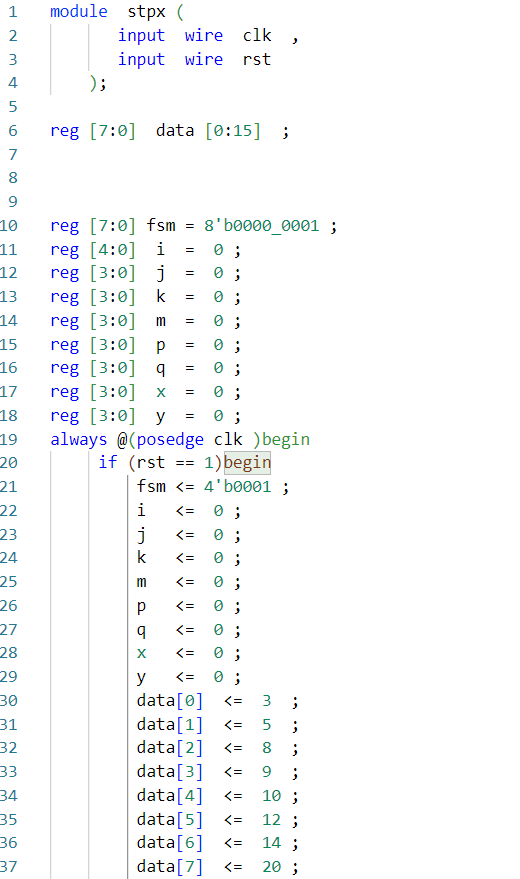

module stpx (

input wire clk ,

input wire rst

);

reg [7:0] data [0:15] ;

reg [7:0] fsm = 8'b0000_0001 ;

reg [4:0] i = 0 ;

reg [3:0] j = 0 ;

reg [3:0] k = 0 ;

reg [3:0] m = 0 ;

reg [3:0] p = 0 ;

reg [3:0] q = 0 ;

reg [3:0] x = 0 ;

reg [3:0] y = 0 ;

always @(posedge clk )begin

if (rst == 1)begin

fsm <= 4'b0001 ;

i <= 0 ;

j <= 0 ;

k <= 0 ;

m <= 0 ;

p <= 0 ;

q <= 0 ;

x <= 0 ;

y <= 0 ;

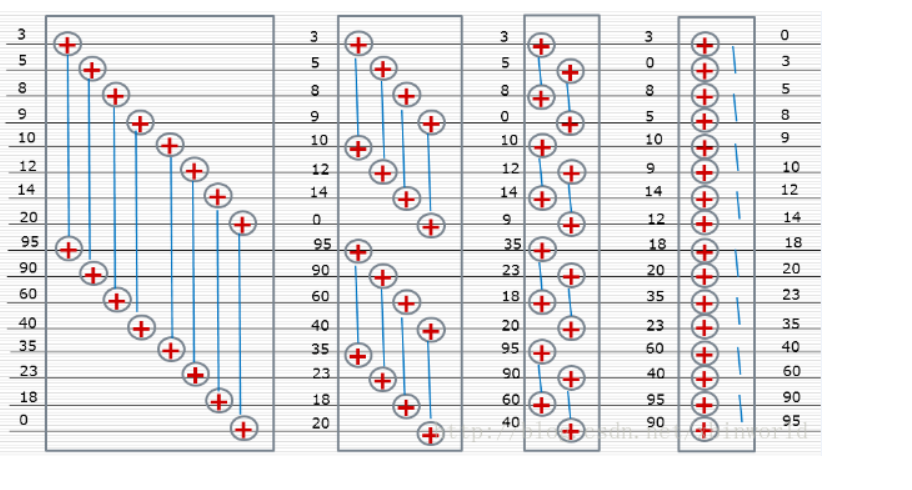

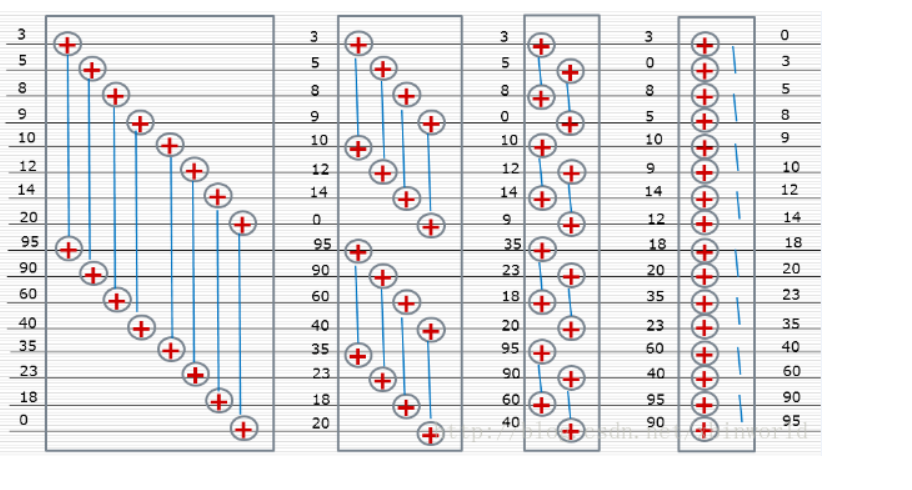

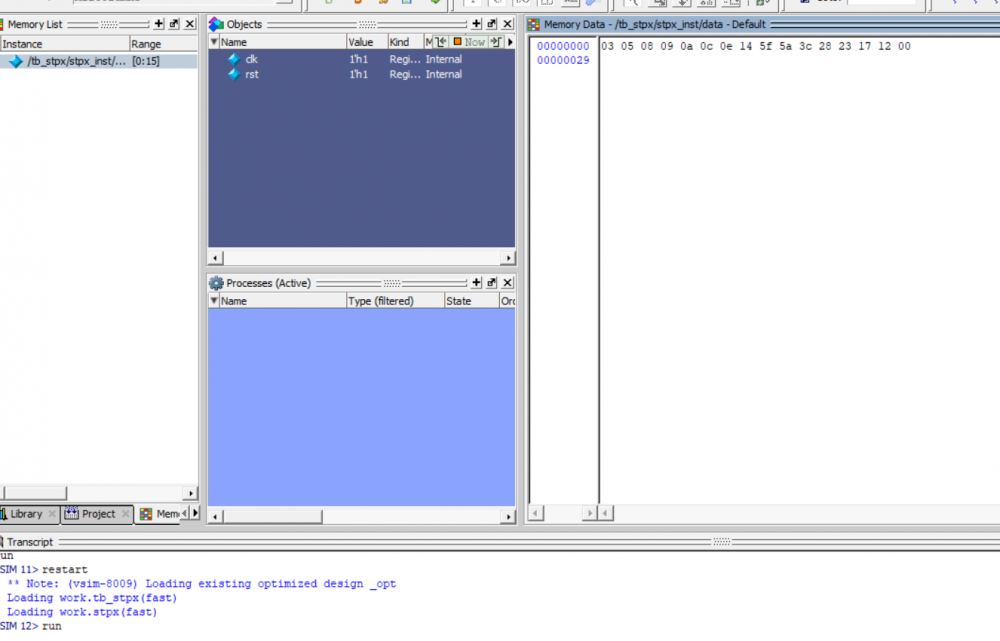

data[0] <= 3 ;

data[1] <= 5 ;

data[2] <= 8 ;

data[3] <= 9 ;

data[4] <= 10 ;

data[5] <= 12 ;

data[6] <= 14 ;

data[7] <= 20 ;

data[8] <= 95 ;

data[9] <= 90 ;

data[10] <= 60 ;

data[11] <= 40 ;

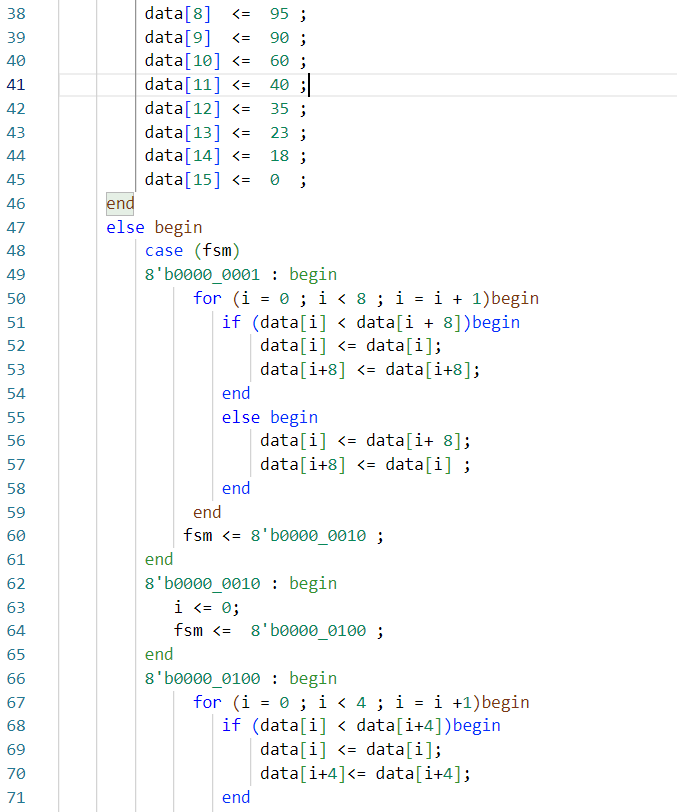

data[12] <= 35 ;

data[13] <= 23 ;

data[14] <= 18 ;

data[15] <= 0 ;

end

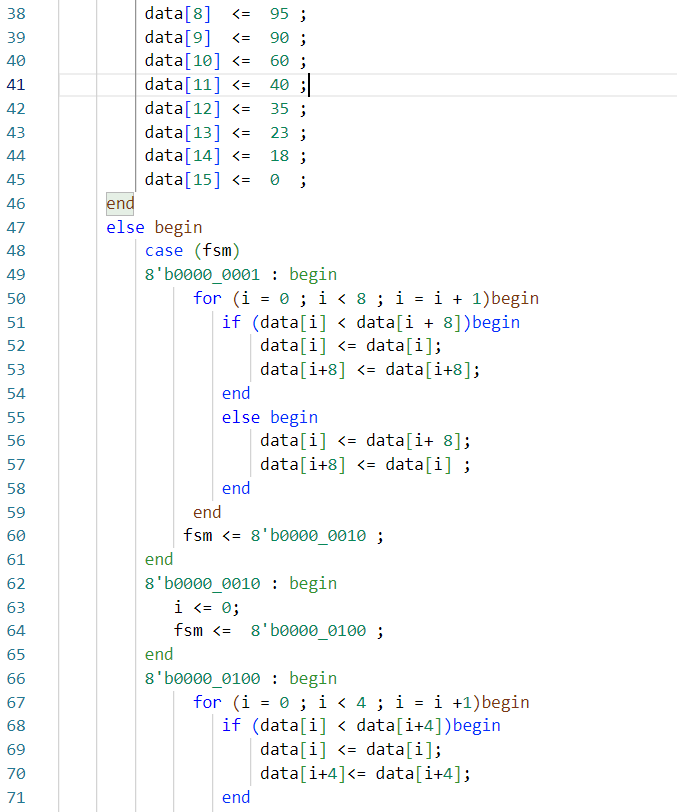

else begin

case (fsm)

8'b0000_0001 : begin

for (i = 0 ; i < 8 ; i = i + 1)begin

if (data[i] < data[i + 8])begin

data[i] <= data[i];

data[i+8] <= data[i+8];

end

else begin

data[i] <= data[i+ 8];

data[i+8] <= data[i] ;

end

end

fsm <= 8'b0000_0010 ;

end

8'b0000_0010 : begin

i <= 0;

fsm <= 8'b0000_0100 ;

end

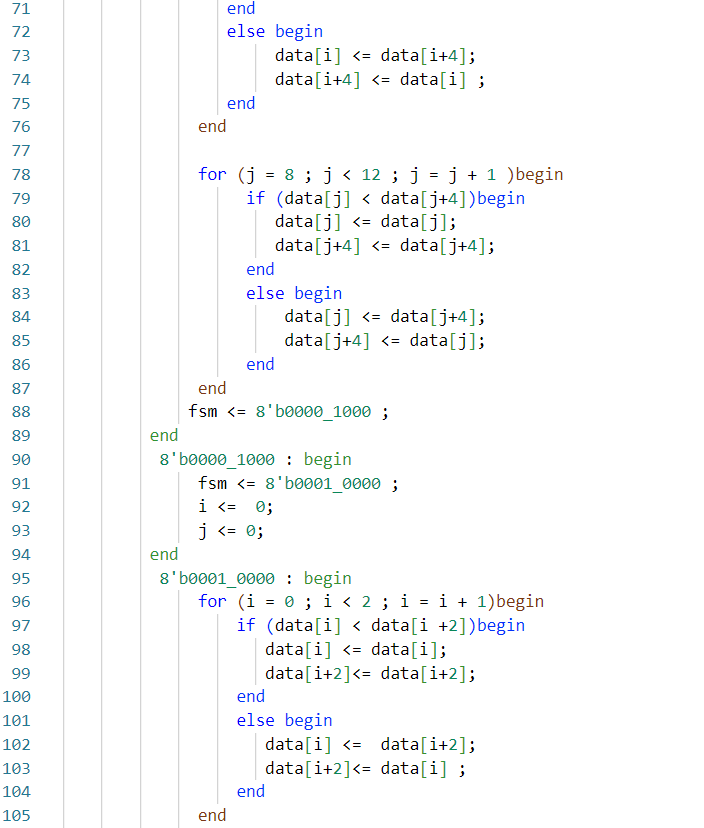

8'b0000_0100 : begin

for (i = 0 ; i < 4 ; i = i +1)begin

if (data[i] < data[i+4])begin

data[i] <= data[i];

data[i+4]<= data[i+4];

end

else begin

data[i] <= data[i+4];

data[i+4] <= data[i] ;

end

end

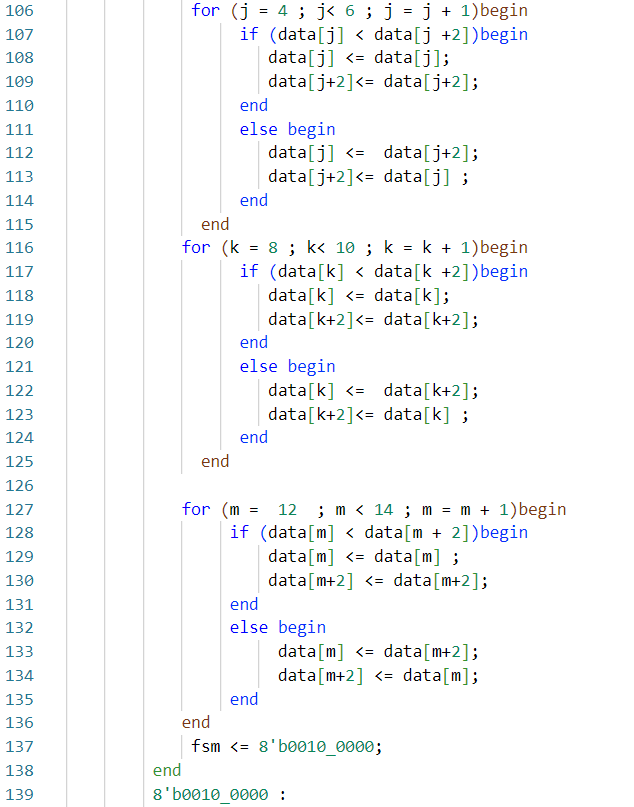

for (j = 8 ; j < 12 ; j = j + 1 )begin

if (data[j] < data[j+4])begin

data[j] <= data[j];

data[j+4] <= data[j+4];

end

else begin

data[j] <= data[j+4];

data[j+4] <= data[j];

end

end

fsm <= 8'b0000_1000 ;

end

8'b0000_1000 : begin

fsm <= 8'b0001_0000 ;

i <= 0;

j <= 0;

end

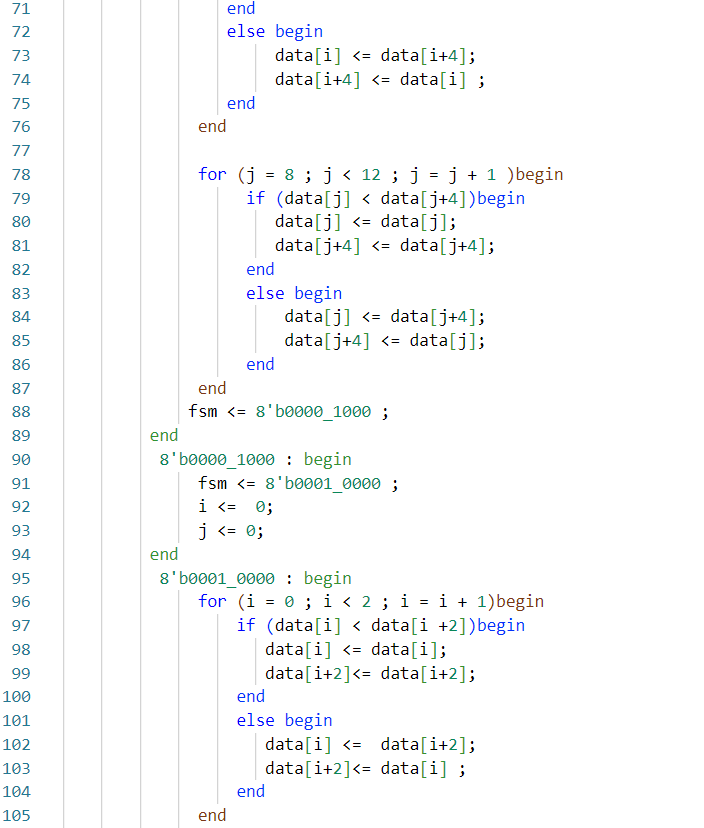

8'b0001_0000 : begin

for (i = 0 ; i < 2 ; i = i + 1)begin

if (data[i] < data[i +2])begin

data[i] <= data[i];

data[i+2]<= data[i+2];

end

else begin

data[i] <= data[i+2];

data[i+2]<= data[i] ;

end

end

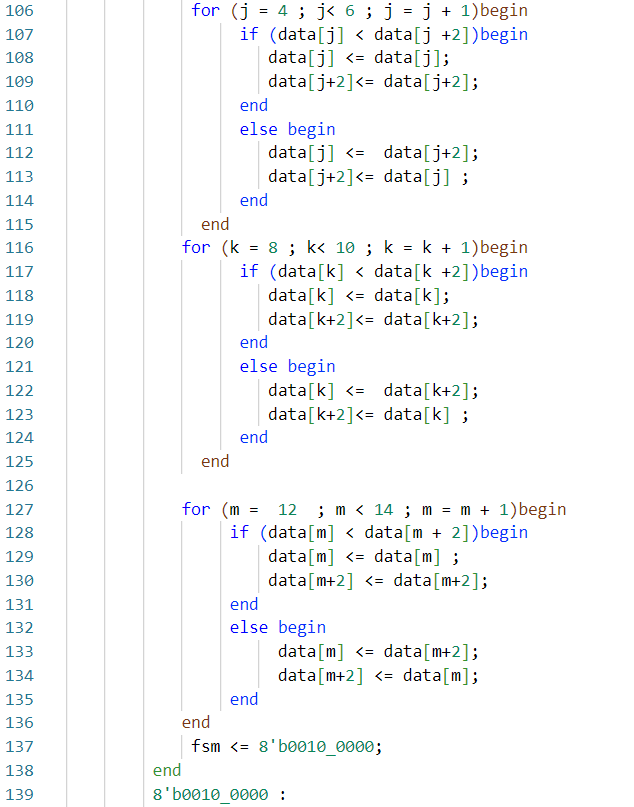

for (j = 4 ; j< 6 ; j = j + 1)begin

if (data[j] < data[j +2])begin

data[j] <= data[j];

data[j+2]<= data[j+2];

end

else begin

data[j] <= data[j+2];

data[j+2]<= data[j] ;

end

end

for (k = 8 ; k< 10 ; k = k + 1)begin

if (data[k] < data[k +2])begin

data[k] <= data[k];

data[k+2]<= data[k+2];

end

else begin

data[k] <= data[k+2];

data[k+2]<= data[k] ;

end

end

for (m = 12 ; m < 14 ; m = m + 1)begin

if (data[m] < data[m + 2])begin

data[m] <= data[m] ;

data[m+2] <= data[m+2];

end

else begin

data[m] <= data[m+2];

data[m+2] <= data[m];

end

end

fsm <= 8'b0010_0000;

end

8'b0010_0000 :

begin

fsm <= 8'b0100_0000 ;

i <= 0 ;

j <= 2 ;

k <= 4 ;

m <= 6 ;

p <= 8 ;

q <= 10 ;

x <= 12 ;

y <= 14 ;

end

8'b0100_0000 : begin

for (i = 0 ; i < 15 ; i = i +2)begin

if (data[i] < data[i+1])begin

data[i] <= data[i];

data[i+1] <= data[i+1];

end

else begin

data[i] <= data[i+1];

data[i+1] <= data[i] ;

end

end

fsm <= 8'b1000_0000;

end

8'b1000_0000 : begin

i <= 0 ;

j <= 0 ;

k <= 0 ;

m <= 0 ;

p <= 0 ;

q <= 0 ;

x <= 0 ;

y <= 0 ;

end

default : begin

fsm <= 8'b0000_0001 ;

end

endcase

end

end

endmodule

________________________________________________________________________________________

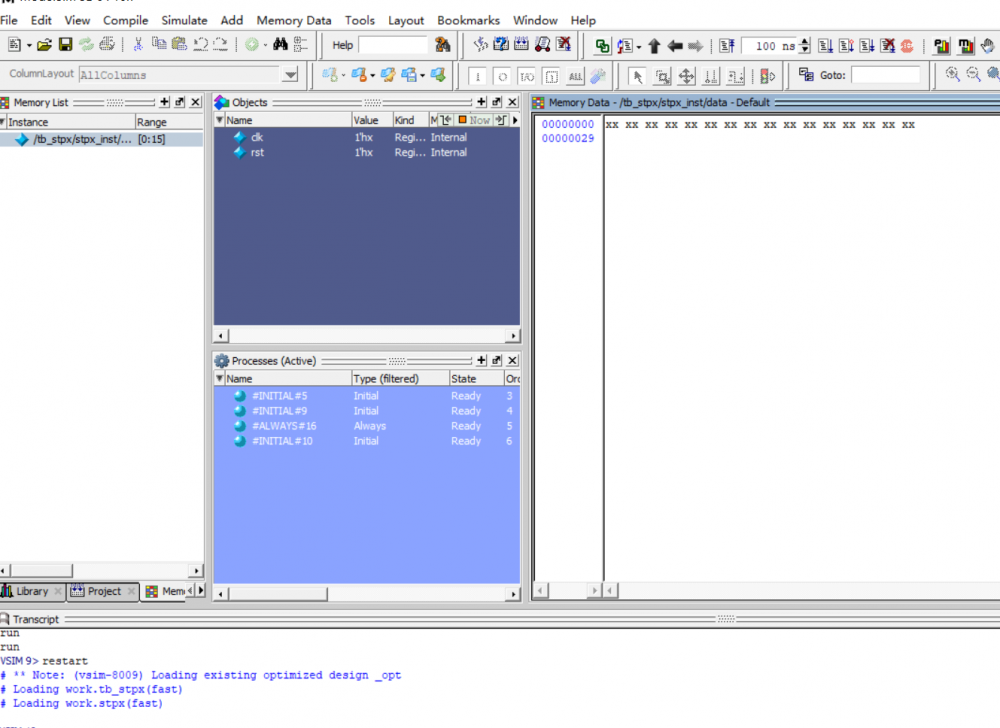

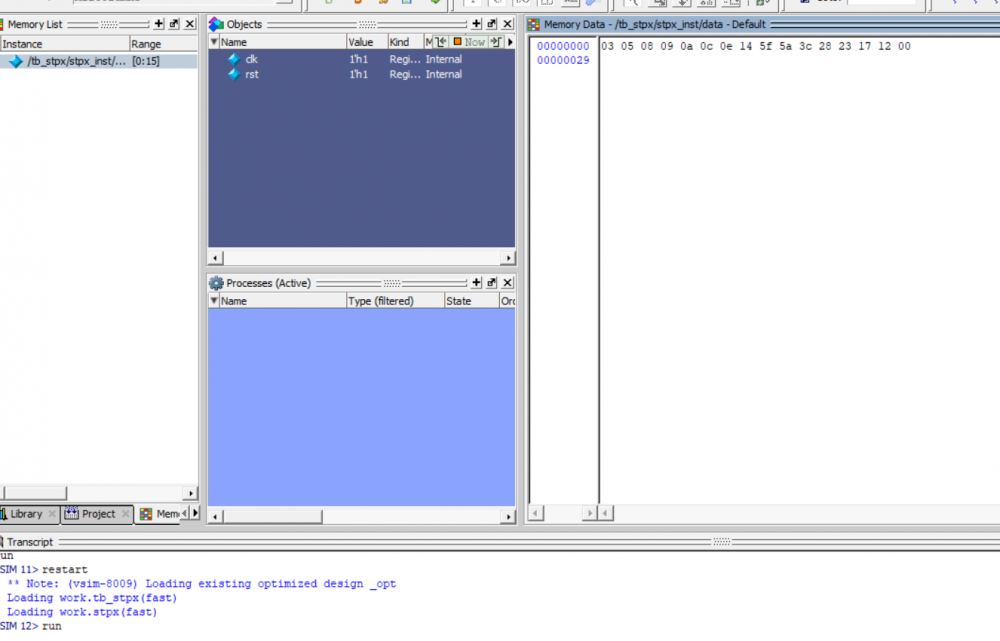

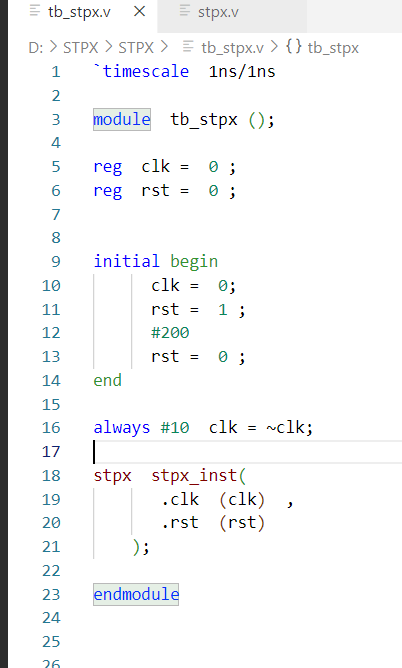

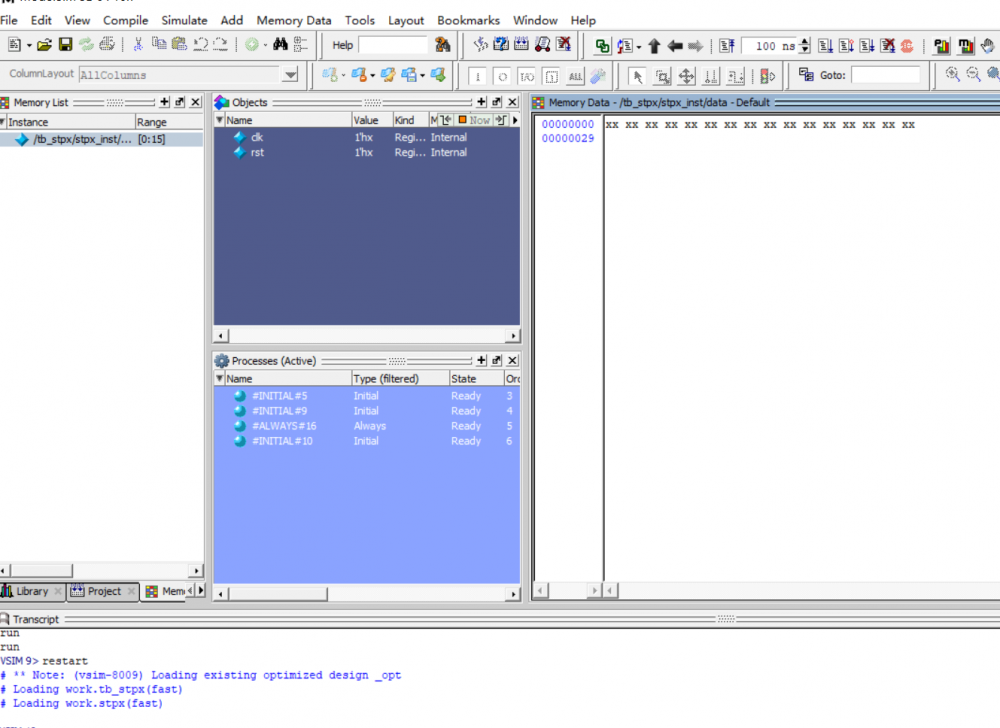

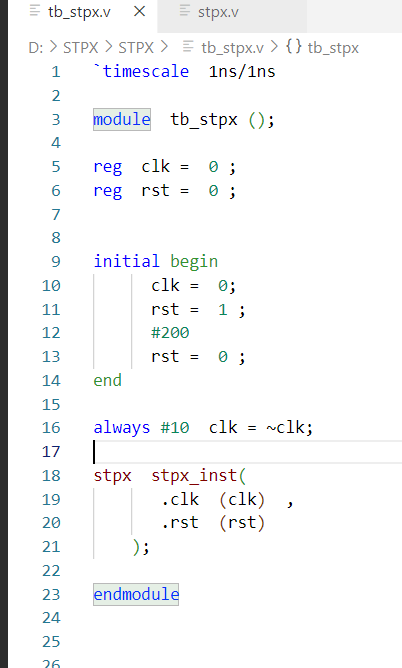

`timescale 1ns/1ns

module tb_stpx ();

reg clk = 0 ;

reg rst = 0 ;

initial begin

clk = 0;

rst = 1 ;

#200

rst = 0 ;

end

always #10 clk = ~clk;

stpx stpx_inst(

.clk (clk) ,

.rst (rst)

);

endmodule

我要赚赏金

我要赚赏金