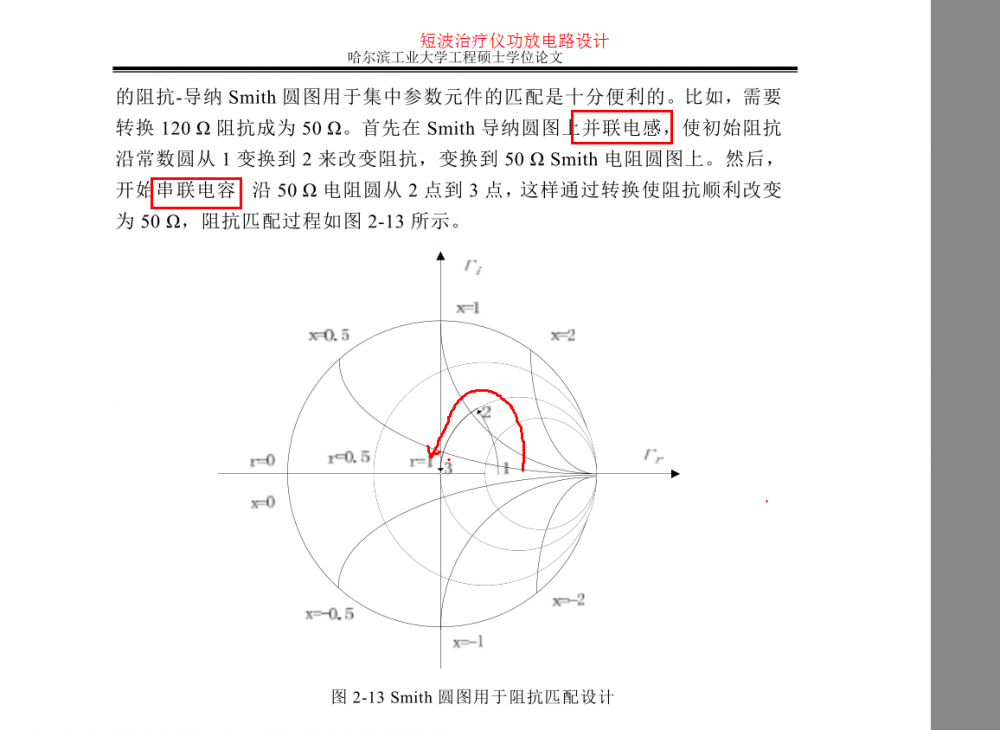

史密斯圆图进行阻抗匹配的过程

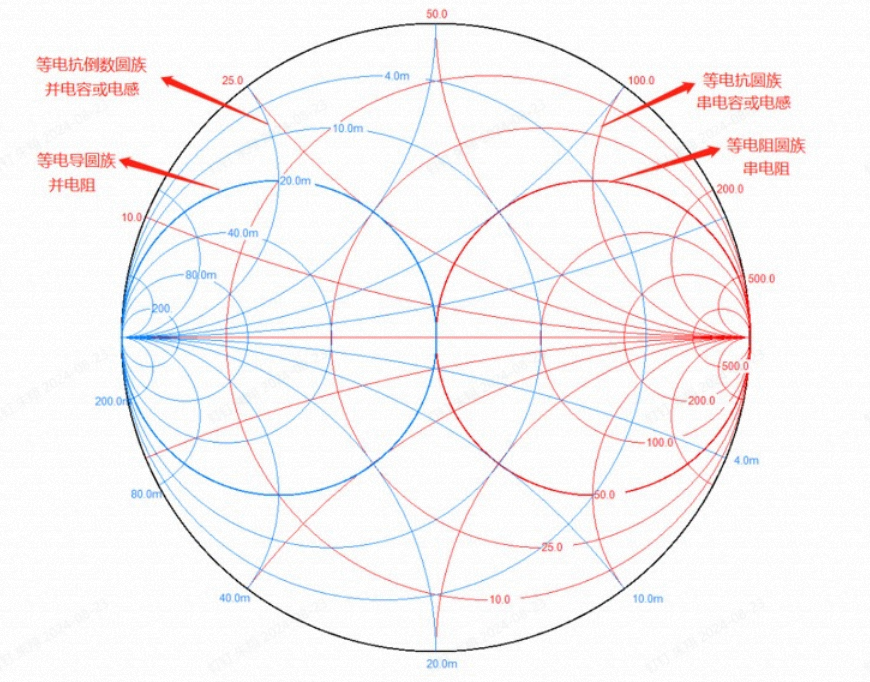

1.为什么要从往上到2点再往下到3点,而不能直接从1到3点?

2.为什么是并联电感、串联电容,这个怎么判断呢?

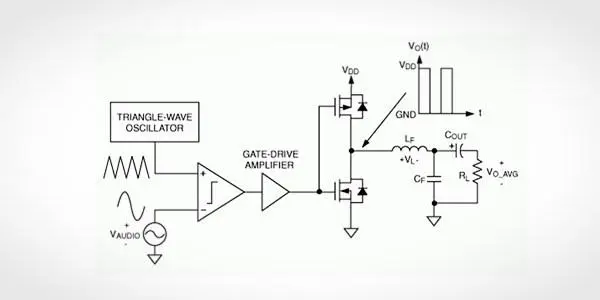

3.假如是D类功放,电路拓扑是一个半桥+LC振荡,LC后面接线缆和负载(比如是超声波换能器)那阻抗的测试过程是先把LC元件从电路板上取下来,测试出半桥的输出阻抗?然后测试出来LC电路、线缆、负载连接在一起的阻抗?最后是调整LC的参数来适配功放的输出阻抗?比如功放输出阻抗是75欧姆,那么把(LC电路+线缆+负载)组件的阻抗调整到75欧姆?具体是怎样的匹配过程?

我要赚赏金

我要赚赏金