在Verilog HDL中,有两大类数据类型:线网类型(Net Type)和变量类型(Variable Type)。这两类数据类型在硬件描述中扮演着不同的角色,主要用于表示电路中的连接和存储元素。

线网类型(Net Type)

线网类型代表了电路中的物理连接,导线或总线。线网的值是由连接到它的驱动元件(连续赋值语句、门的输出等)决定的。如果没有任何驱动元件连接到线网,线网的缺省值依赖于上下文,但通常不是直接指定的,因为线网需要外部驱动来赋予其值。不过,在某些情况下,可以通过属性(tristate、pullup、pulldown等)来影响线网的默认行为,但这些并不是直接通过类型定义来设置的。

列举一些常见的线网类型:

wire:最基本的线网类型,用于表示单向连接。 tri(或triwire):三态线网,表示高、低或高阻态(Z)。 wand 和 wor:这两个类型不是标准Verilog中的直接类型,通过连续赋值语句使用与(AND)或或(OR)逻辑来模拟。 triand 和 trilor:这些也不是直接的类型,通过三态逻辑门来模拟与和或的行为。 @supply0 和 @supply1:这些不是标准的Verilog线网类型,是在某些特定环境或工具中的扩展,用于表示连接到电源地(0)或电源(1)的连线。 trireg:结合了tri和寄存器(reg)的特性,注意的是,trireg并不是所有Verilog工具都支持的标准类型,且其行为可能因工具而异。

变量类型(Variable Type)

变量类型代表了抽象的数据存储单元,通常用于在过程块(always和initial块)中存储临时值。变量的值在每次赋值语句执行时更新,并且保持该值直到下一次赋值。变量类型的缺省值为x。

声明线网的简单语法

对于线网的声明,通常的语法如下:

[net_type] [signed] [range] list_of_nets;

其中:

net_type 是线网的类型, wire、tri 等。

signed 是可选的,表示线网是否有符号。

range 是可选的,定义了线网的位宽,格式为 [msb:lsb]。

list_of_nets 是要声明的线网名称列表,用逗号分隔。

举例:

wire [7:0] data_bus, address_bus; // 声明两个8位宽的线网 trireg tri_reg_example; // 声明一个三态寄存器类型的线网(注意:这可能不是所有工具都支持)

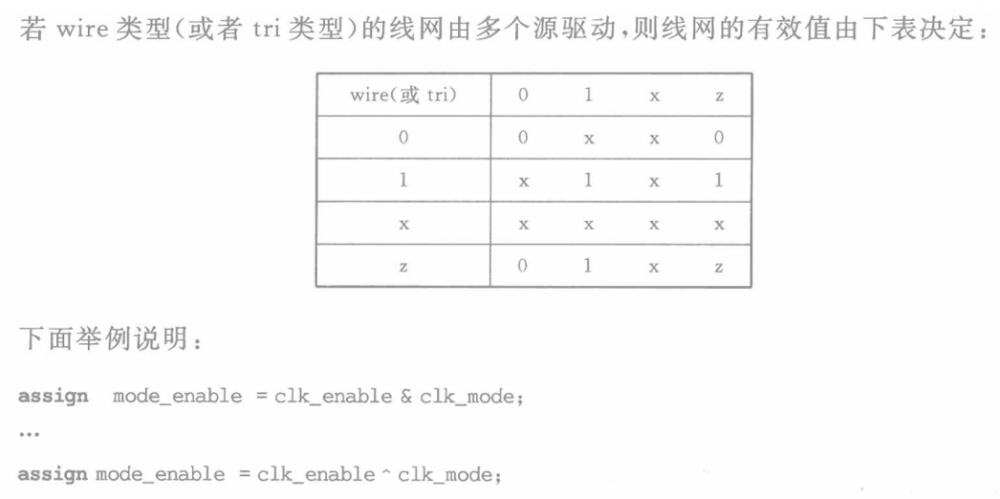

wire 类型

wire类型是最基本的线网类型,用于表示电路中的单向连接。它可以被连续赋值语句(assign语句)或模块的输出直接驱动。如果wire被多个源驱动,并且这些源的值不一致(一个为0,另一个为1),则wire的值将变为x(未知)或z(高阻态),具体取决于上下文和Verilog版本/仿真器的行为。

tri 类型

tri(三态)类型用于表示可以处于高、低或高阻态(Z)的线网。这在模拟总线或具有三态输出的设备时非常有用。在现代Verilog设计中,tri类型的使用已经变得不那么常见了,因为许多现代仿真器和合成工具可能不完全支持或优化这种类型的线网。

关于多个源驱动的问题

mode_enable由两个源(clk_enable和clk_mode)驱动,并试图通过一种真值表来决定其值。Verilog标准并不直接支持通过真值表来合并多个源对wire或tri的驱动。

实际上,如果mode_enable被设计为同时由clk_enable和clk_mode通过连续赋值语句(assign)来驱动,这通常是错误的,因为这会导致竞争条件或未定义行为。assign语句被重复使用了,但通常只能为一个wire或tri指定一个assign语句。

基于clk_enable和clk_mode的值来计算mode_enable的值,使用单个assign语句,并通过逻辑运算符(&(与)、|(或)、^(异或)等)来组合这两个信号。

举例:

assign mode_enable = clk_enable & clk_mode; // 使用与运算符 // 或者 assign mode_enable = clk_enable ^ clk_mode; // 使用异或运算符 mode_enable应该是一个标量(单一位的信号),而不是向量(多位的信号),为mode_enable的每个位分别计算值,但这通常不是通过单个assign语句来实现的,而是需要为每个位编写单独的赋值逻辑。

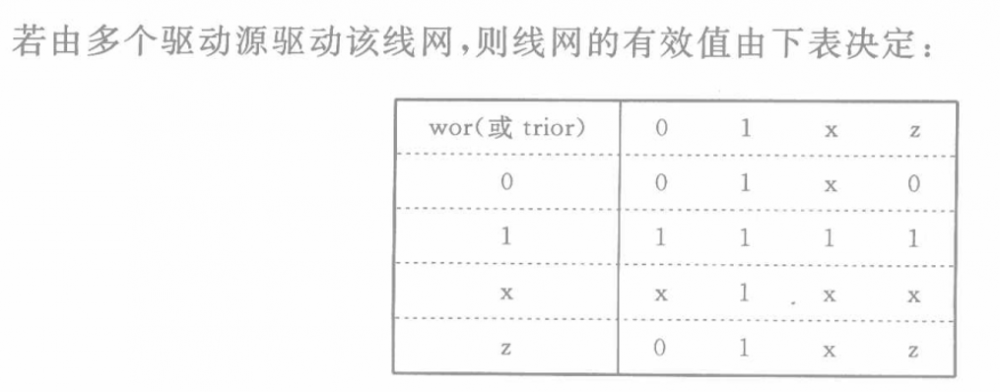

在Verilog中,wor 并不是一个标准的线网(net)类型。谈论类似“线或”(wire-OR)的行为时,我们是在描述一种逻辑功能,即当多个信号源中的任何一个为高(1)时,输出线网也会为高(1)。在Verilog的标准类型中,并没有直接称为 wor 的类型。

相反,这种“线或”的行为通常是通过逻辑运算符或连续赋值语句来实现的。对于单个线网,可以使用 assign 语句和逻辑或运算符(|)来模拟 wor 的行为。要一个更通用的解决方案,特别是当有多个这样的“线或”线网时,可能会考虑使用模块或生成块来组织的代码。

至于 trior,它同样不是一个标准的Verilog线网类型。有些仿真器或特定工具可能会实现自己的扩展类型来支持三态逻辑下的“或”操作。这种类型并不是Verilog IEEE标准的一部分,它的行为可能因工具而异。

在标准Verilog中,如果想要实现三态逻辑下的“或”操作,需要自己编写逻辑来处理三态(Z)的情况。这通常涉及到检查每个驱动源的值,并根据这些值以及它们是否处于三态来决定输出值。

一个简化的“线或”(包括三态情况)的行为如下:

如果任何一个驱动源为1,则输出为1。

如果所有驱动源都是0或Z(高阻态),则输出取决于是否有Z状态存在。在某些情况下,如果所有源都是Z,则输出也可能是Z;但在其他情况下,如果至少有一个源是0且没有其他源为1,则输出可能是0(这取决于的具体需求和仿真器的行为)。

如果任何驱动源为X(未知),则输出通常为X,因为未知值会传播。

但是,请注意,这个表格和描述是简化的,并且可能不完全符合任何特定仿真器的实际行为。

在标准Verilog中,可以使用类似以下的代码来模拟“线或”的行为(但不包括三态逻辑的直接支持):

wire [MAX-1:MIN-1] ctrl_reg; // 假设有一个或多个源来驱动 ctrl_reg,但这里我们只展示一个例子 assign ctrl_reg = source1 | source2 | ... | sourceN; // 使用逻辑或运算符 // 注意:这里没有直接处理三态逻辑(Z),因为Verilog的wire类型不支持直接的三态逻辑操作。 // 如果需要处理三态逻辑,可能需要定义一个模块来封装这种逻辑。

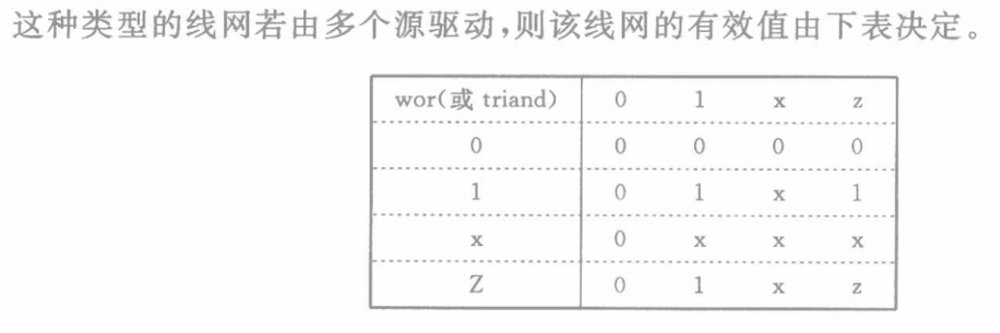

在Verilog中,wand(Wire AND,即线与)和triand(三态线与)同样不是标准的线网(net)类型。不过,我们可以理解这些术语所描述的逻辑行为。

wand(线与)指的是当多个信号源通过逻辑与(AND)操作连接到一起时,如果任何一个信号源为0,则整个线网的输出值为0。这种逻辑在硬件设计中很常见,特别是在需要确保所有条件都满足时才能激活某个信号的场景中。

由于Verilog没有内置的wand类型,使用连续赋值语句(assign)和逻辑与运算符(&)来模拟这种行为。

类似地,triand(三态线与)指的是在wand的基础上增加了对三态(Z,高阻态)的支持。但是,由于Verilog标准线网类型不支持直接的三态逻辑与操作,需要自己编写逻辑来处理这种情况。

表格中,试图展示wor(或triand,但根据上下文应该是triand的误写)的行为,但表格的内容并不完全准确或清晰。根据描述给出一个简化的wand(以及假设的triand)行为的说明。

对于wand:

如果所有驱动源都为1,则输出为1。

如果任何一个驱动源为0,则输出为0。

如果任何驱动源为X(未知)或Z(高阻态),则输出可能依赖于仿真器的具体实现,但通常X会传播到输出,而Z可能需要特别处理(通过模块逻辑将其视为0或保持未知)。

对于假设的triand(注意这不是标准类型):

如果所有非Z的驱动源都为1,且没有X,则输出为1。

如果任何一个非Z的驱动源为0,则输出为0(无论其他源是什么)。

如果存在X,则输出通常为X(未知传播)。

如果所有驱动源都是Z,则输出可能也是Z,或者在某些情况下可能需要特别处理(通过外部逻辑决定输出)。

请注意,由于triand不是标准类型,需要自己编写逻辑来模拟这种行为。这通常涉及到检查每个驱动源的状态,并根据这些状态来决定输出。

在Verilog中,可以使用类似以下的代码来模拟wand的行为:

wire [7:0] paddress; // 假设有多个源来驱动 paddress,但这里只展示一个例子 assign paddress = source1 & source2 & ... & sourceN; // 使用逻辑与运算符 // 对于 triand,由于它不是标准类型,需要自定义逻辑 // 这通常涉及到在一个模块内部实现这个逻辑

在Verilog中,提到的trireg、tri0、tri1、supply0和supply1线网类型并不是Verilog IEEE标准中的直接类型。这些术语可能用于描述某些特定于工具或模拟环境的高级特性或建模技术。下面我将根据描述解释这些概念以及它们在Verilog环境中可能的用法。

4. trireg 线网

trireg并不是一个标准的Verilog线网类型。不过,从描述来看,它似乎是一个能够存储数值并且具有三态(高阻态Z)能力的线网类型。在标准的Verilog中,没有直接名为trireg的类型,可以通过结合使用寄存器(reg)和特定的赋值逻辑来模拟这种行为。

当所有驱动源都处于高阻态(Z)时,保持上一个有效值的行为通常需要通过代码逻辑来实现,而不是自动发生的。

缺省初始值在Verilog中通常是未定义的(X),除非显式地为其赋予一个初始值。

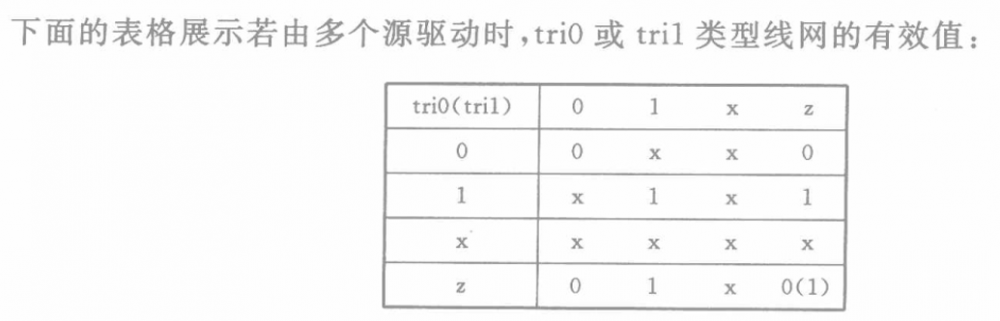

5. tri0 和 tri1 线网

这些也不是标准的Verilog线网类型,但可以根据描述进行理解:

tri0:当没有驱动源或所有驱动源都为高阻态时,输出默认为0。 tri1:当没有驱动源或所有驱动源都为高阻态时,输出默认为1。

在标准的Verilog中,可以通过编写连续赋值语句或使用生成块来模拟这种行为。

表格说明

提供的表格尝试展示tri0和tri1线网在多个源驱动下的有效值,但表格格式在文本中难以完全展示。不过,可以概括地说,tri0在没有有效驱动时输出0,而tri1输出1。如果存在任何非Z的驱动源,则输出由这些源的逻辑运算决定(尽管对于tri0和tri1来说,这种逻辑运算可能是隐式的,因为它们主要关注缺省值)。

6. supply0 和 supply1 线网

这些类型通常用于建模电源和地线:

supply0:代表地线(VSS),其值始终为0。 supply1:代表电源线(VDD),其值始终为1(或在模拟电源电压的上下文中为电源电压的等效逻辑值)。

在Verilog中,这些通常不需要显式声明为特殊类型的线网,可以直接在需要的地方使用数字0和1来表示地线和电源线。

在一些模拟环境中,可能需要特殊的声明来建模电源的电气特性。

总结

虽然trireg、tri0、tri1不是Verilog标准中的类型,可以通过编写适当的代码来模拟这些行为。supply0和supply1在建模电源和地线时非常有用,但它们通常不需要特殊的线网类型,而是直接通过常数值来表示。

正在使用特定的仿真工具或硬件描述语言(HDL)扩展,请查阅该工具的文档以了解如何正确使用这些非标准类型。

我要赚赏金

我要赚赏金