在Verilog中,变量类型是用来定义存储数据的类型及其特性(位宽、符号性等)的。

Verilog中的变量类型Verilog中主要有两大类变量:线网(net) 和 寄存器(register) 类型。

一些特殊类型的变量,参数(parameter)、整数(integer)、时间(time)等。主要关注寄存器类型中的reg类型,以及与之相关的概念。

Verilog HDL 语法虽然有很多,真正常用的却屈指可数, 只需要掌握了常用的语法,就可以用 Verilog HDL 语言去描述逻辑电路。

下面开始介绍,一种是 wire(线型),另一种是 reg(寄存器型)。

在数字电路中信号只有两种形态,一种是传输,一种是存储。传输是通过连接线, 存储是用寄存器,在 Verilog HDL 中常用 wire 和 reg 变量了。

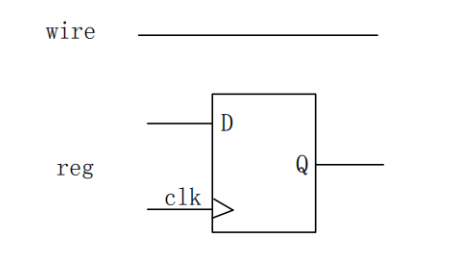

wire 和 reg 变量模型如图所示:

上图中,wire 型变量在物理结构上只是一根线,对线型变量赋值用 assign,相对比较简单。图中reg 型变量左端有一个D输入端口,右端有一个Q输出端口, 并且 reg 型存储数据需要在 clk(时钟)沿的控制下完成,

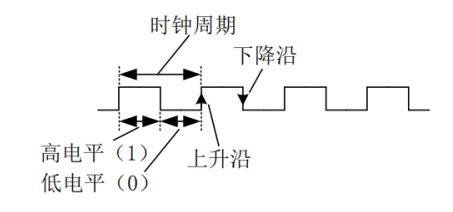

它是由晶振产生,是我们描述数字电路时最基本的时间单元,它的周期固定,占空比一般为 50%(即高电平占整个周期的比例)。

clk 的低电平用数字 0 表示,高电平用 1 表示,从低电平转变到高电平的过程叫做上升沿,从高电平转变到低电平的过程叫做下降沿,如下图所示。

可以指定位宽,也可以不指定(默认为1位)。reg类型的变量可以被赋值多次。

• reg [3:0] ext_bus; // 4位无符号变量 • reg signed [7:0] signed_byte; // 8位有符号变量 • reg test_rega; // 1位无符号变量 • reg [3:0] ext_bus; // 声明一个4位无符号reg变量 • initial ext_bus = 4'b0001; // 在initial块中初始化 • // 或者,在声明时尝试初始化(注意,这取决于Verilog的具体版本或编译器) • // reg [3:0] ext_bus = 4'b0001; // 可能不被所有编译器支持

更常见的做法是在initial块或always块中初始化。

• 默认值:未初始化的reg类型变量的默认值是x(未知)或z(高阻态),这取决于上下文。在仿真开始时,这些值通常被设置为x或z,直到它们被明确赋值。

2. 其他提到的类型• integer:这是另一种常用的变量类型,用于存储整数。与reg不同,integer类型的变量不能用于硬件描述中的线网连接,主要用于仿真中的计数、常用于计数器、循环控制、算术运算等。

• nteger类型用于存储整数值,常用于仿真中的计数器和算术运算。它不能用于硬件描述中的线网连接,因为integer变量在仿真过程中可以变化,而硬件中的线网连接是静态的。• integer counter; • always @(posedge clk) counter = counter + 1;

• time:用于存储时间值,常用于仿真中的时间控制。常用于仿真中的时间控制,延迟和测量。

• real 和 realtime:这些类型在Verilog中并不直接作为变量类型出现。real类型在SystemVerilog中被引入,用于存储浮点数。而realtime是SystemVerilog中与real类型相关的时间单位,但在纯Verilog中并不存在。

real类型用于存储浮点数,这在需要高精度数值计算的仿真中非常有用。

realtime是SystemVerilog中与real类型相关的时间单位,用于表示时间间隔的浮点数。

3. 符号性和位宽

• 符号性:通过在reg声明前添加signed关键字,可以指定变量为有符号数。默认情况下,reg变量是无符号的。

• 位宽:通过[msb:lsb]语法可以指定变量的位宽,其中msb是最高位(最左边的位),lsb是最低位(最右边的位)。如果未指定位宽,则默认为1位。

• 符号性:通过在reg声明前添加signed关键字,可以指定变量为有符号数。这在进行有符号数的算术运算时非常有用。

module test;

reg [3:0] ext_bus; // 4位无符号变量

reg signed [7:0] byte; // 8位有符号变量

integer counter; // 整数变量,用于计数

time delay; // 时间变量,用于控制延迟

initial begin

ext_bus = 4'b0001; // 初始化ext_bus

counter = 0; // 初始化counter

delay = 10ns; // 设置延迟时间为10纳秒

// 模拟过程

#delay; // 等待10纳秒

counter = counter + 1; // 计数器加1

$display("ext_bus = %b, counter = %d", ext_bus, counter);

end

endmodule总结:

Verilog中的reg类型是一种非常灵活且强大的数据类型,用于在仿真过程中表示可变的值。通过结合符号性和位宽控制,reg类型可以精确地模拟各种硬件信号和变量。

了解integer、time等其他类型以及它们在仿真中的应用也是非常重要的。

随着SystemVerilog的普及,一些在Verilog中不存在的类型(如real和realtime)也在更高级的仿真和验证任务中发挥着作用。

我要赚赏金

我要赚赏金