简介:

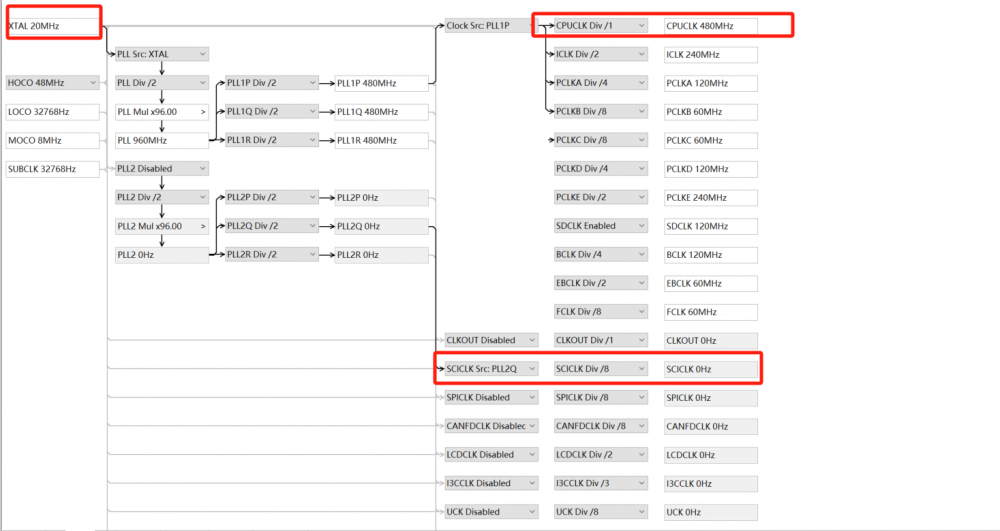

瑞萨的RA Smart Configurator 的工具跟ST的STM32CubeMX 工具类似都是可以使用图形化的配置工具生成配置代码,RA Smart Configurator 工具也可以自动的添加freertos 等,相对来说该工具做的还是比较完善的,我们创建工程的时候选择适配freertos 的工程配置,创建好后我们配置时钟源为外部XTAL,并配置CPU 运行在48M,因为要使用串口SCI模块在此开启SCI clock。

该配置对应生成的clock 初始化配置代码如下:

/* generated configuration header file - do not edit */ #ifndef BSP_CLOCK_CFG_H_ #define BSP_CLOCK_CFG_H_ #define BSP_CFG_CLOCKS_SECURE (0) #define BSP_CFG_CLOCKS_OVERRIDE (0) #define BSP_CFG_XTAL_HZ (20000000) /* XTAL 20000000Hz */ #define BSP_CFG_HOCO_FREQUENCY (7) /* HOCO 48MHz */ #define BSP_CFG_PLL_SOURCE (BSP_CLOCKS_SOURCE_CLOCK_MAIN_OSC) /* PLL Src: XTAL */ #define BSP_CFG_PLL_DIV (BSP_CLOCKS_PLL_DIV_2) /* PLL Div /2 */ #define BSP_CFG_PLL_MUL BSP_CLOCKS_PLL_MUL(96,0) /* PLL Mul x80-99|Mul x96|PLL Mul x96.00 */ #define BSP_CFG_PLL_FREQUENCY_HZ (960000000) /* PLL 960000000Hz */ #define BSP_CFG_PLODIVP (BSP_CLOCKS_PLL_DIV_2) /* PLL1P Div /2 */ #define BSP_CFG_PLL1P_FREQUENCY_HZ (480000000) /* PLL1P 480000000Hz */ #define BSP_CFG_PLODIVQ (BSP_CLOCKS_PLL_DIV_2) /* PLL1Q Div /2 */ #define BSP_CFG_PLL1Q_FREQUENCY_HZ (480000000) /* PLL1Q 480000000Hz */ #define BSP_CFG_PLODIVR (BSP_CLOCKS_PLL_DIV_2) /* PLL1R Div /2 */ #define BSP_CFG_PLL1R_FREQUENCY_HZ (480000000) /* PLL1R 480000000Hz */ #define BSP_CFG_PLL2_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* PLL2 Disabled */ #define BSP_CFG_PLL2_DIV (BSP_CLOCKS_PLL_DIV_2) /* PLL2 Div /2 */ #define BSP_CFG_PLL2_MUL BSP_CLOCKS_PLL_MUL(96,0) /* PLL2 Mul x80-99|Mul x96|PLL2 Mul x96.00 */ #define BSP_CFG_PLL2_FREQUENCY_HZ (0) /* PLL2 0Hz */ #define BSP_CFG_PL2ODIVP (BSP_CLOCKS_PLL_DIV_2) /* PLL2P Div /2 */ #define BSP_CFG_PLL2P_FREQUENCY_HZ (0) /* PLL2P 0Hz */ #define BSP_CFG_PL2ODIVQ (BSP_CLOCKS_PLL_DIV_2) /* PLL2Q Div /2 */ #define BSP_CFG_PLL2Q_FREQUENCY_HZ (0) /* PLL2Q 0Hz */ #define BSP_CFG_PL2ODIVR (BSP_CLOCKS_PLL_DIV_2) /* PLL2R Div /2 */ #define BSP_CFG_PLL2R_FREQUENCY_HZ (0) /* PLL2R 0Hz */ #define BSP_CFG_CLOCK_SOURCE (BSP_CLOCKS_SOURCE_CLOCK_PLL1P) /* Clock Src: PLL1P */ #define BSP_CFG_CLKOUT_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* CLKOUT Disabled */ #define BSP_CFG_SCICLK_SOURCE (BSP_CLOCKS_SOURCE_CLOCK_PLL1Q) /* SCICLK Src: PLL1Q */ #define BSP_CFG_SPICLK_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* SPICLK Disabled */ #define BSP_CFG_CANFDCLK_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* CANFDCLK Disabled */ #define BSP_CFG_LCDCLK_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* LCDCLK Disabled */ #define BSP_CFG_I3CCLK_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* I3CCLK Disabled */ #define BSP_CFG_UCK_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* UCK Disabled */ #define BSP_CFG_U60CK_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* U60CK Disabled */ #define BSP_CFG_OCTA_SOURCE (BSP_CLOCKS_CLOCK_DISABLED) /* OCTASPICLK Disabled */ #define BSP_CFG_CPUCLK_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_1) /* CPUCLK Div /1 */ #define BSP_CFG_ICLK_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_2) /* ICLK Div /2 */ #define BSP_CFG_PCLKA_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_4) /* PCLKA Div /4 */ #define BSP_CFG_PCLKB_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_8) /* PCLKB Div /8 */ #define BSP_CFG_PCLKC_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_8) /* PCLKC Div /8 */ #define BSP_CFG_PCLKD_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_4) /* PCLKD Div /4 */ #define BSP_CFG_PCLKE_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_2) /* PCLKE Div /2 */ #define BSP_CFG_SDCLK_OUTPUT (1) /* SDCLK Enabled */ #define BSP_CFG_BCLK_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_4) /* BCLK Div /4 */ #define BSP_CFG_BCLK_OUTPUT (2) /* EBCLK Div /2 */ #define BSP_CFG_FCLK_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_8) /* FCLK Div /8 */ #define BSP_CFG_CLKOUT_DIV (BSP_CLOCKS_SYS_CLOCK_DIV_1) /* CLKOUT Div /1 */ #define BSP_CFG_SCICLK_DIV (BSP_CLOCKS_SCI_CLOCK_DIV_8) /* SCICLK Div /8 */ #define BSP_CFG_SPICLK_DIV (BSP_CLOCKS_SPI_CLOCK_DIV_4) /* SPICLK Div /4 */ #define BSP_CFG_CANFDCLK_DIV (BSP_CLOCKS_CANFD_CLOCK_DIV_8) /* CANFDCLK Div /8 */ #define BSP_CFG_LCDCLK_DIV (BSP_CLOCKS_LCD_CLOCK_DIV_2) /* LCDCLK Div /2 */ #define BSP_CFG_I3CCLK_DIV (BSP_CLOCKS_I3C_CLOCK_DIV_3) /* I3CCLK Div /3 */ #define BSP_CFG_UCK_DIV (BSP_CLOCKS_USB_CLOCK_DIV_5) /* UCK Div /5 */ #define BSP_CFG_U60CK_DIV (BSP_CLOCKS_USB60_CLOCK_DIV_5) /* U60CK Div /5 */ #define BSP_CFG_OCTA_DIV (BSP_CLOCKS_OCTA_CLOCK_DIV_4) /* OCTASPICLK Div /4 */ #endif /* BSP_CLOCK_CFG_H_ */

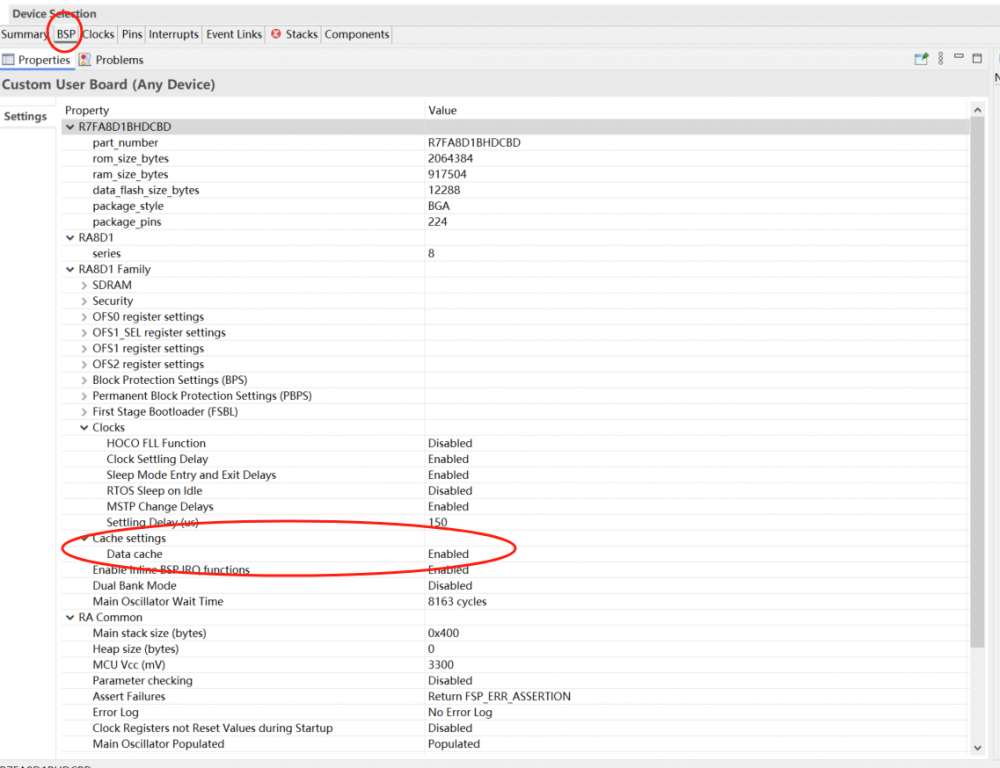

在BSP 窗口下可以配置芯片的运行参数,为了提高芯片的执行速率在该窗口下开启Dcache。

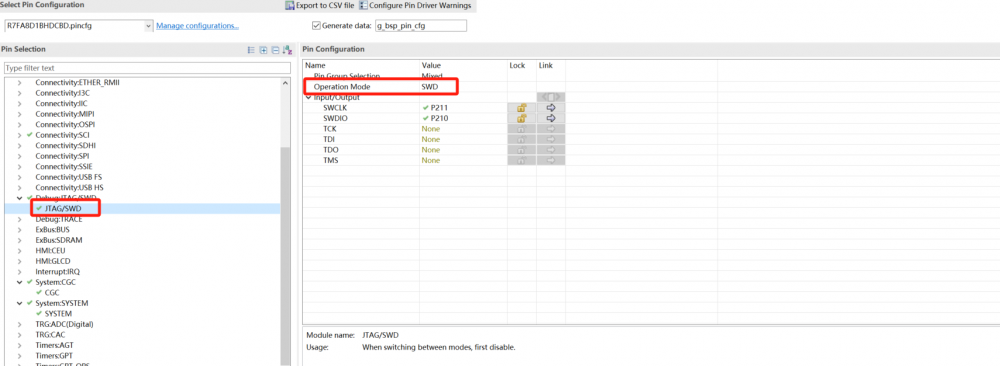

Pin 窗口下根据板子的配置修改调试接口为SWD

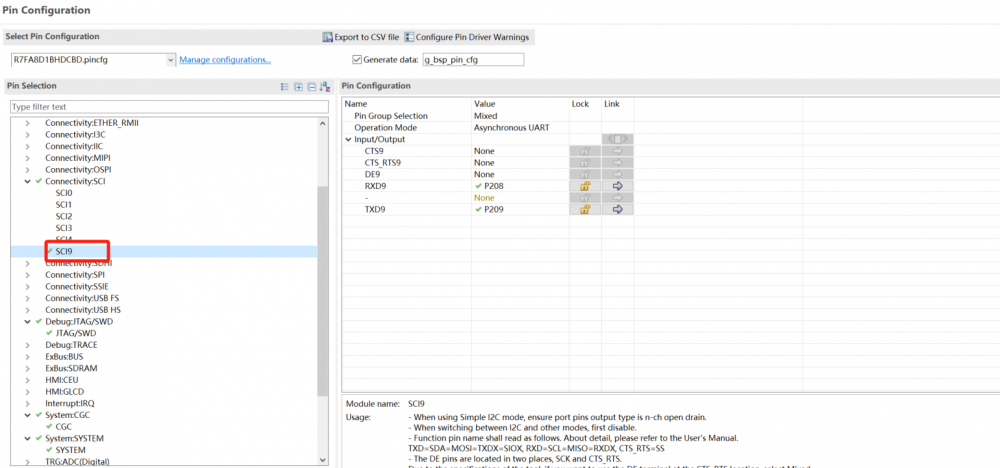

配置要输出串口log 的Pin 引脚。

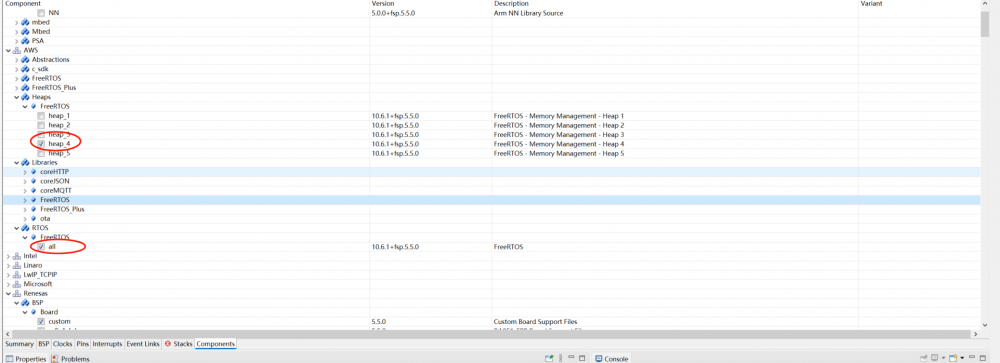

Componnets 下选择freertos 的heap 分配算法及Freertos.

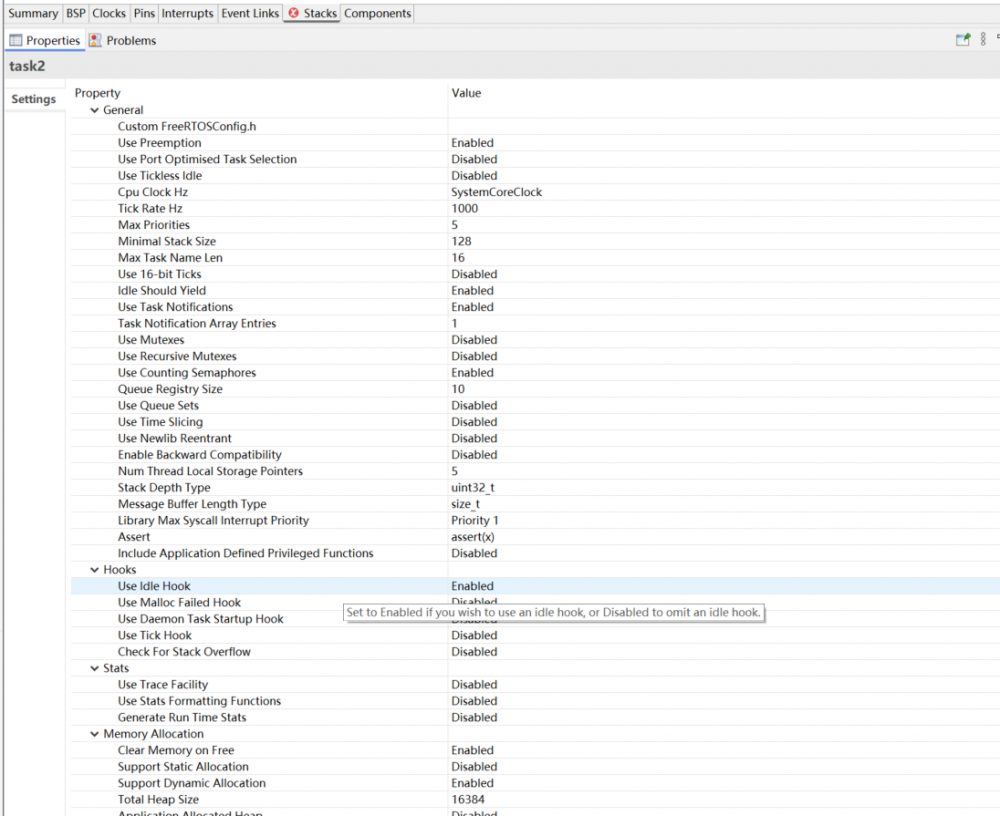

配置freertos 参数配置该参数会生成freertos 的配置文件。

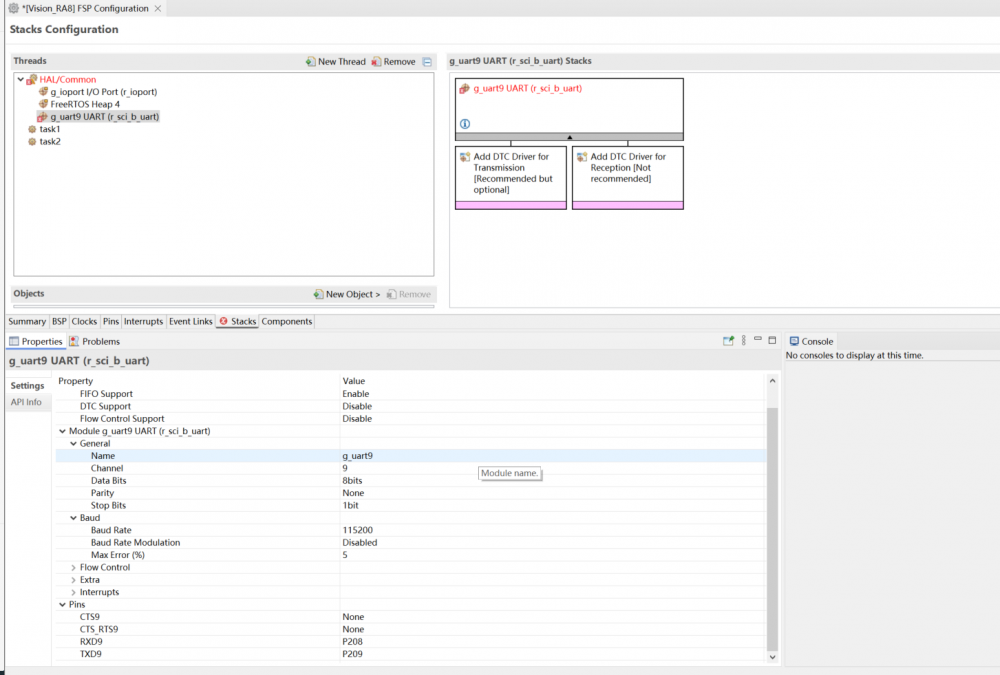

配置SCI9 uart 的输出参数

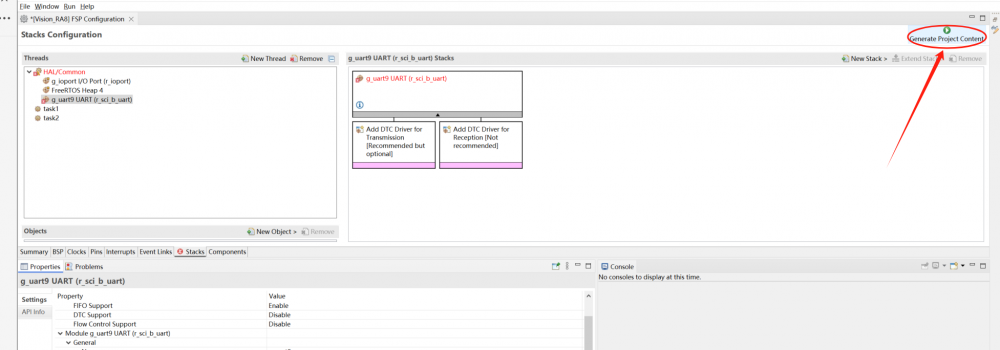

之后点击此按钮生成工程及SDK 时钟、uart、bsp 等初始化配置代码。

添加如下代码将printf 输出对接至uart9.

size_t __write(int hand, const unsigned char * buff, size_t size)

{

int i_loop;

sci_b_uart_instance_ctrl_t *p_ctrl = (sci_b_uart_instance_ctrl_t *)g_uart9.p_ctrl;

for(i_loop = 0;i_loop < size;i_loop++)

{

while ((p_ctrl->p_reg->CSR_b.TEND) == 0);

p_ctrl->p_reg->TDR = buff[i_loop];

}

return size;

}将上述的生成的配置文件加入工程编译,并创建以下任务切换测试代码。

void start_task(void *pvParameters)

{

while(1)

{

printf("task1 \r\n");

R_IOPORT_PinWrite(&g_ioport_ctrl,BSP_IO_PORT_01_PIN_02,BSP_IO_LEVEL_HIGH);

vTaskDelay(1000);

R_IOPORT_PinWrite(&g_ioport_ctrl,BSP_IO_PORT_01_PIN_02,BSP_IO_LEVEL_LOW);

vTaskDelay(1000);

}

}

void task2(void *pvParameters)

{

while(1)

{

printf("task2 \r\n");

R_IOPORT_PinWrite(&g_ioport_ctrl,BSP_IO_PORT_01_PIN_06,BSP_IO_LEVEL_HIGH);

vTaskDelay(1000);

R_IOPORT_PinWrite(&g_ioport_ctrl,BSP_IO_PORT_01_PIN_06,BSP_IO_LEVEL_LOW);

vTaskDelay(1000);

}

}

int main(void)

{

R_SCI_B_UART_Open(g_uart9.p_ctrl,g_uart9.p_cfg);

xTaskCreate((TaskFunction_t )start_task,

(const char* )"task1",

(uint16_t )START_STK_SIZE,

(void* )NULL,

(UBaseType_t )START_TASK_PRIO,

(TaskHandle_t* )&StartTask_Handler);

xTaskCreate((TaskFunction_t )task2,

(const char* )"task2",

(uint16_t )LVGL_STK_SIZE,

(void* )NULL,

(UBaseType_t )LVGL_TASK_PRIO,

(TaskHandle_t* )&LvglTask_Handler);

vTaskStartScheduler();

}下载到板子中运行发现task1 和 task2 会轮流打印,说明freertos 已经正常调度运行。

我要赚赏金

我要赚赏金