Cortex-M3/M4的寄存器之中断屏蔽特殊寄存器

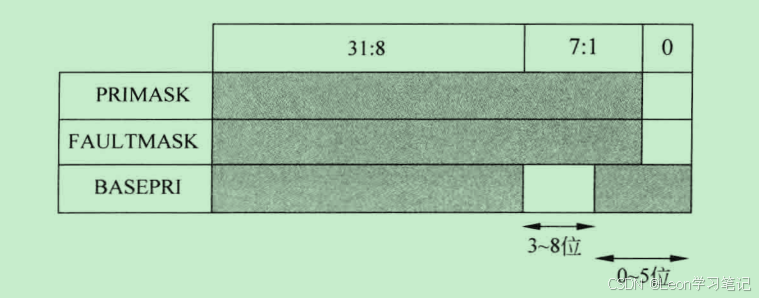

PRIMASK、FAULTMASK 和 BASEPRI寄存器都用于异常或中断屏蔽,每个异常(包括中断)都具有一个优先等级,数值小的优先级高,而数值大的则优先级低。这些特殊寄存器可基于优先等级屏蔽异常,只有在特权访问等级才可以对它们进行操作(非特权状态下的写操作会被忽略,而读出则会返回 0)。它们默认全部为0,也就是屏蔽(禁止异常/中断)不起作用。

PRIMASK寄存器为1位宽的中断屏蔽寄存器。在置位时,它会阻止不可屏蔽中断(NMI)和 HardFault 异常之外的所有异常(包括中断)。实际上,它是将当前异常优先级提升为0,这也是可编程异常/中断的最高优先级。

PRIMASK 最常见的用途为,在时间要求很严格的进程中禁止所有中断,在该进程完成后,需要PRIMASK 清除以重新使能中断。

FAULTMASK 和 PRIMASK 非常类似,不过它还能屏蔽 HardFault 异常,它实际上是将异常优先级提升到了-1。错误处理代码可以使用FAULTMASK以免在错误处理期间引发其他的错误(只有几种)。例如,FAULTMASK 可用于旁路 MPU 或屏蔽总线错误(这些都是可配置的),这样,错误处理代码执行修复措施也就更加容易了。与PRIMASK 不同,FAULTMASK 在异常返回时会被自动清除。

为使中断屏蔽更加灵活,ARMv7-M架构还支持BASEPRI,该寄存器会根据优先等级屏蔽异常或中断。BASEPRI的宽度取决于设计实际实现的优先级数量,这是由微控制器供应商决定的。大多数 Cortex-M3 或 Cortex-M4 微控制器都有8个(3 位宽)或 16 个可编程的异常优先级,此时,BASEPRI的宽度就相应地为3位或4位。BASEPRI为0时就不会起作用当被设置为非0数值时,它就会屏蔽具有相同或更低优先级的异常(包括中断),而更高优先级的则还可以被处理器接受。

CMSIS-Core 提供了多个C函数用于访问 PRIAMSK、FAULTMASK及 BASEPRI 寄存器(注意,这些寄存器只能在特权等级下访问)。

X=_get_BASEPRI();//读BASEPRI寄存器 X=_get_PRIMARK();//读PRIMASK寄存器 X =_get_FAULTMASK();//读FAULTMASK寄存器 _set_BASEPRI(x);//设置 BASEPRI 的新数值 _set_PRIMASK(x);//设置 PRIMASK的新数值 _set_FAULTMASK(x);//设置 FAULTMASK 的新数值 _disable_irq();//设置PRIMASK,禁止IRQ _enable_irg();//清除PRIMASK,使能 IRO

注意 FAULTMASK和BASEPRI寄存器在ARMv6-M中不存在(如 Cortex-MO)。

我要赚赏金

我要赚赏金