【简介】

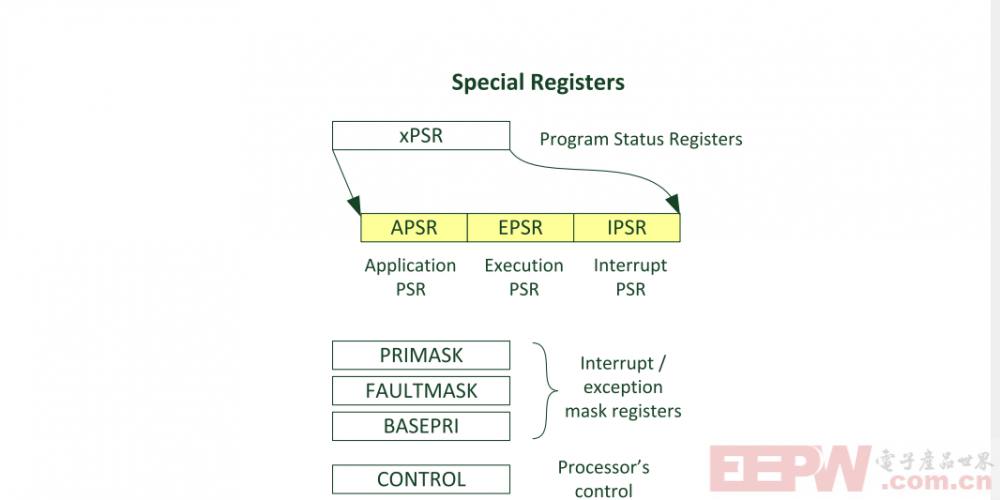

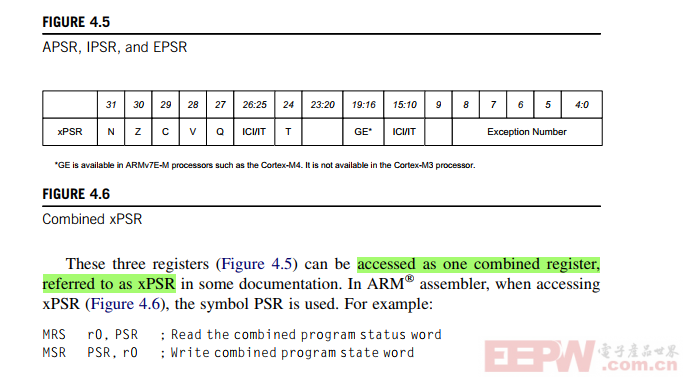

Cortex-M 架构下XPSR(Program status registers),是Application PSR (APSR),Execution PSR (EPSR),Interrupt PSR (IPSR) 寄存器的合称,上述三个状态该寄存器合并为xPSR寄存器,对应的layout 如下。

对于xPSR寄存器的访问可以使用MSR/MSR指令进行读写访问

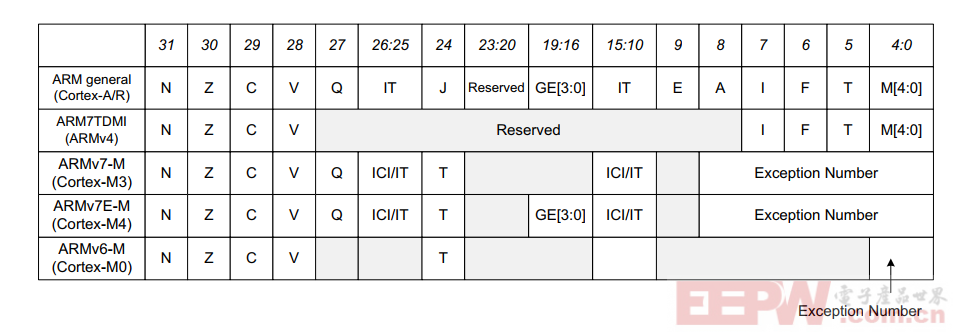

xPSR的定义和ARM架构有关,以下是不同架构下xPSR寄存器定义的差异

查看CORTEX-M0 的芯片的xPSR 只有NZCV/Exception Number/T 的定义

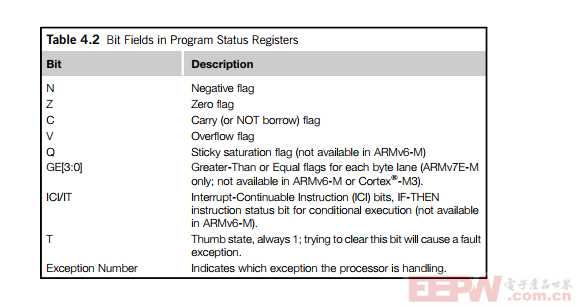

各个信号的说明如下

其中APSR 的 NZCV 状态主要用于记录当前ALU的计算状态,根据NZCV的状态程序可以进行条件判断,对应的条件判断和APSR 的状态位的关系如下。

对于ARM-M处理器的条件执行可以查看之前的介绍帖子ARM CortexM 系列处理器汇编指令执行条件梳理

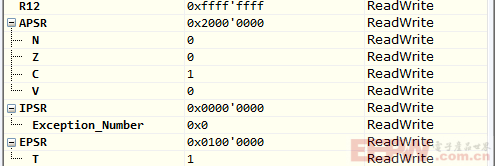

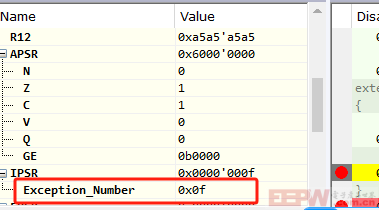

IPSR 寄存器会记录当前正在处理的中断号,本地在systick 中断函数内添加断点,查看对应的IPSR信息为0x0f

0x0f 正好是systick 的中断号

EPSR.T 在Cortex-M 架构中只支持thumb status,如果修改为1后触发hardfault,我们在IAR 环境下修改该值为0,发现跟预期的一样进入hardfault,从IAR 的hardfault 信息窗口也可以看出,异常原因为进入了无效的状态。

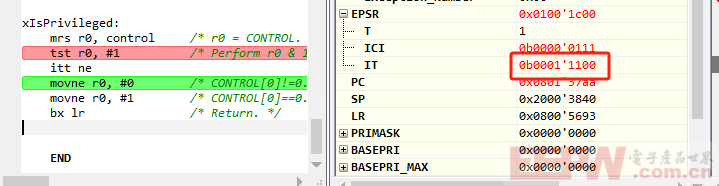

ICI/IT 段会在IF-THEN 指令上下文时更新IT指令的状态

为了验证该机制,我们编写如下测试代码

xIsPrivileged: mrs r0, control /* r0 = CONTROL. */ tst r0, #1 /* Perform r0 & 1 (bitwise AND) and update the conditions flag. */ itt ne movne r0, #0 /* CONTROL[0]!=0. Return false to indicate that the processor is not privileged. */ movne r0, #1 /* CONTROL[0]==0. Return true to indicate that the processor is privileged. */ bx lr

运行该部分代码后发现对应的寄存器已经置位

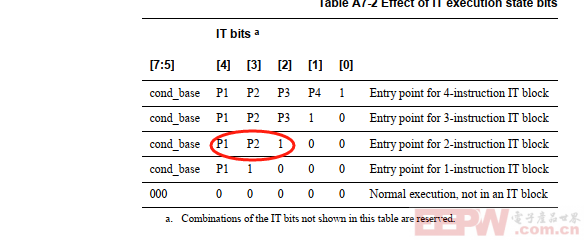

从IF-THEN 的指令编码为两条指令块的IT 指令。

我要赚赏金

我要赚赏金