【简介】

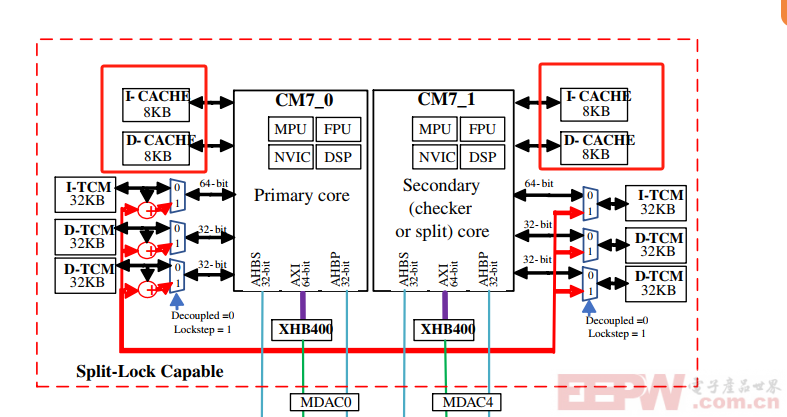

S32K314 内部集成了8KB 的L1 DCACHE ,DCACHE 设计时参数为4-way 64-set cacheline size 32B, 32B(cacheline)*64(set)*4(way) = 8192B(8KB),S32K314 芯片为CORTEX-M7内核对应的架构为ARMV7-M。

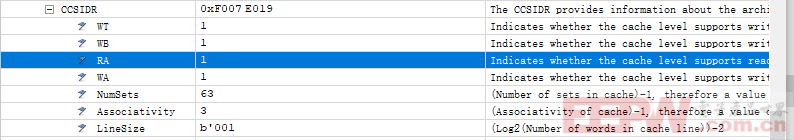

对应DCACHE ICACHE 信息如下

I-Cache L1: 8 KB, 128 Sets, 32 Bytes/Line, 2-Way D-Cache L1: 8 KB, 64 Sets, 32 Bytes/Line, 4-Way

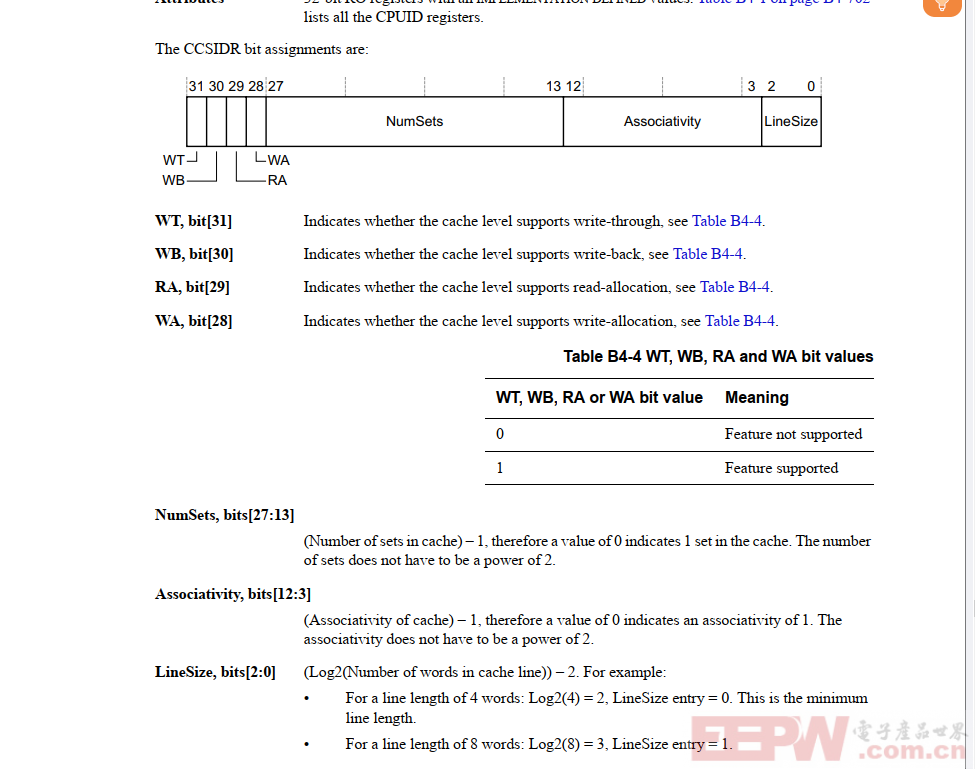

在M7 的手册中也有对L1 cahce 的set/way 的信息描述

以下是CACHE 的数据管理的框图,后续代码中会涉及到Cache 的way/set /line的概念

【CACHE INIT】

以下接口为cache init 的代码内容

static INLINE void sys_m7_cache_init(void)

{

#ifdef D_CACHE_ENABLE

uint32 ccsidr = 0U;

uint32 sets = 0U;

uint32 ways = 0U;

/*init Data caches*/

S32_SCB->CSSELR = 0U; /* select Level 1 data cache */

ASM_KEYWORD("dsb");

ccsidr = S32_SCB->CCSIDR;

sets = (uint32)(CCSIDR_SETS(ccsidr));

do {

ways = (uint32)(CCSIDR_WAYS(ccsidr));

do {

S32_SCB->DCISW = (((sets << SCB_DCISW_SET_Pos) & SCB_DCISW_SET_Msk) |

((ways << SCB_DCISW_WAY_Pos) & SCB_DCISW_WAY_Msk) );

ASM_KEYWORD("dsb");

} while (ways-- != 0U);

} while(sets-- != 0U);

ASM_KEYWORD("dsb");

S32_SCB->CCR |= (uint32)SCB_CCR_DC_Msk; /* enable D-Cache */

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

#endif /*D_CACHE_ENABLE*/

#ifdef I_CACHE_ENABLE

/*init Code caches*/

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

S32_SCB->ICIALLU = 0UL; /* invalidate I-Cache */

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

S32_SCB->CCR |= (uint32)SCB_CCR_IC_Msk; /* enable I-Cache */

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

#endif /*I_CACHE_ENABLE*/

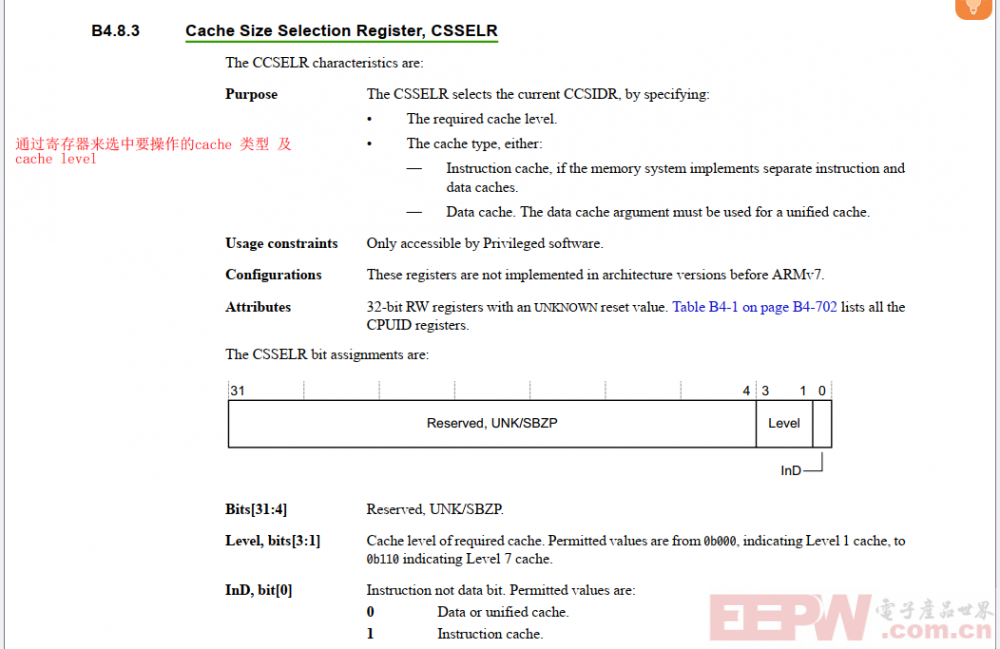

}对应如下代码选中要操作的CACHE 为L1 data cache

/*init Data caches*/

S32_SCB->CSSELR = 0U; /* select Level 1 data cache */

ASM_KEYWORD("dsb");CSSELR 对应寄存器描述如下

ccsidr = S32_SCB->CCSIDR;

sets = (uint32)(CCSIDR_SETS(ccsidr));

do {

ways = (uint32)(CCSIDR_WAYS(ccsidr));

do {

S32_SCB->DCISW = (((sets << SCB_DCISW_SET_Pos) & SCB_DCISW_SET_Msk) |

((ways << SCB_DCISW_WAY_Pos) & SCB_DCISW_WAY_Msk) );

ASM_KEYWORD("dsb");

} while (ways-- != 0U);

} while(sets-- != 0U);

ASM_KEYWORD("dsb");

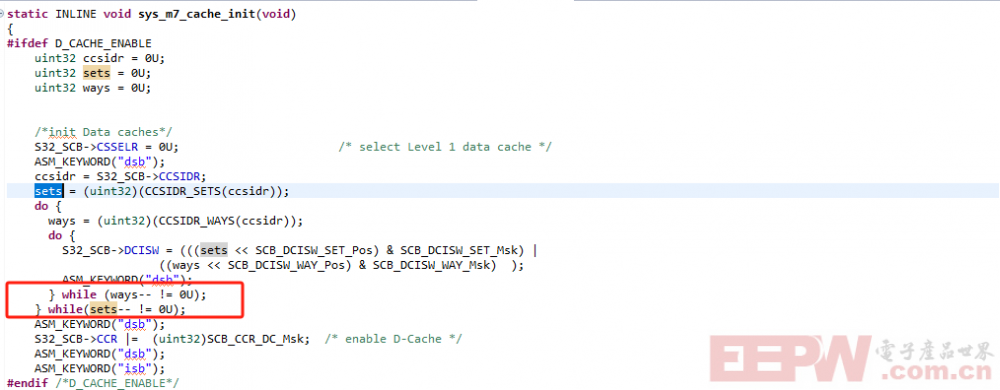

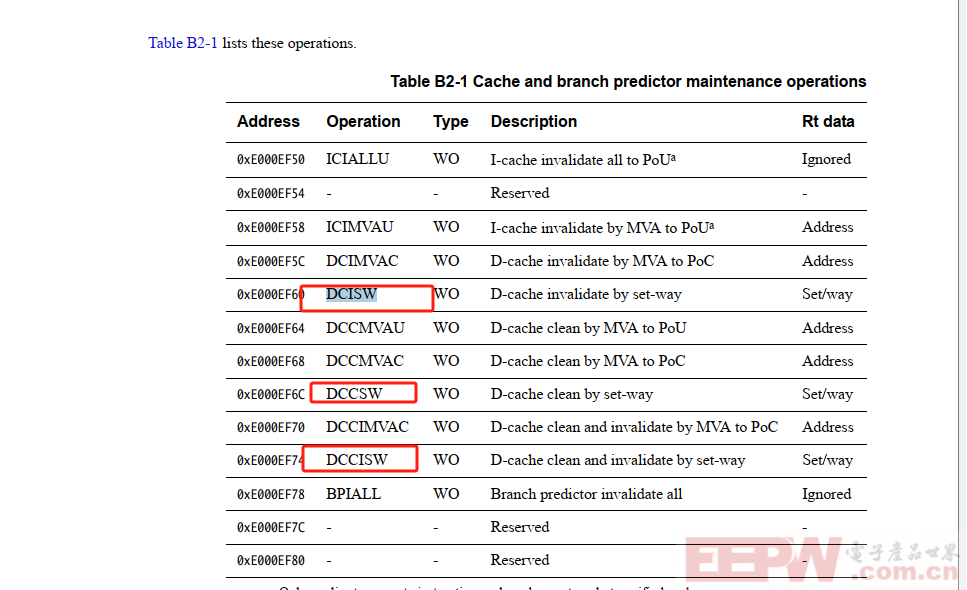

上述代码根据芯片设计时的way/set 信息通过DCISW 寄存器invalue 对应的cache line

上述代码按照set 遍历将对应的way 中的set cache line 无效。

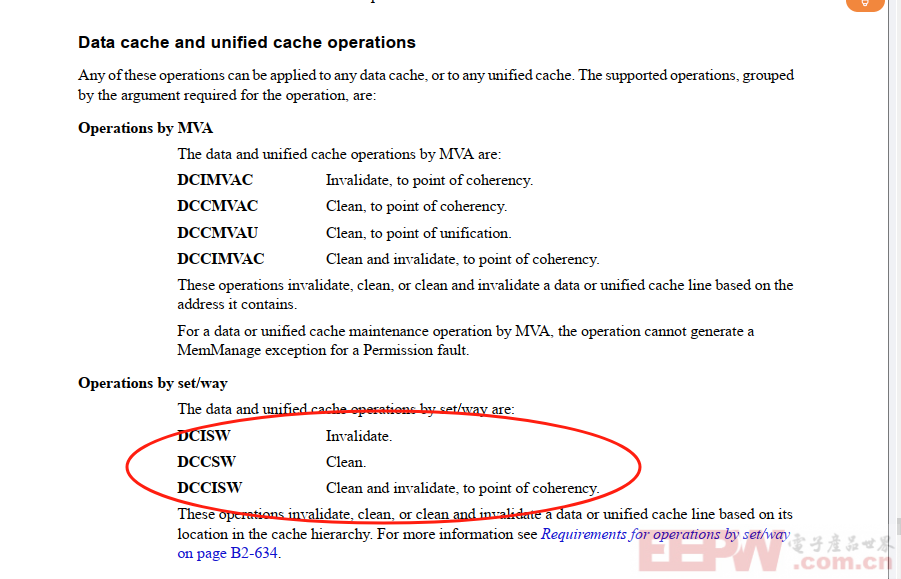

可以使用DCISW/DCCSW/DCCISW 寄存器来操作cache

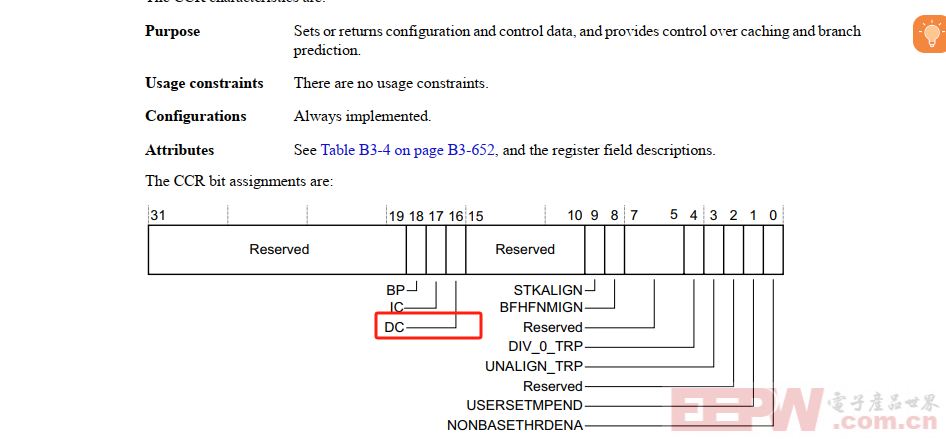

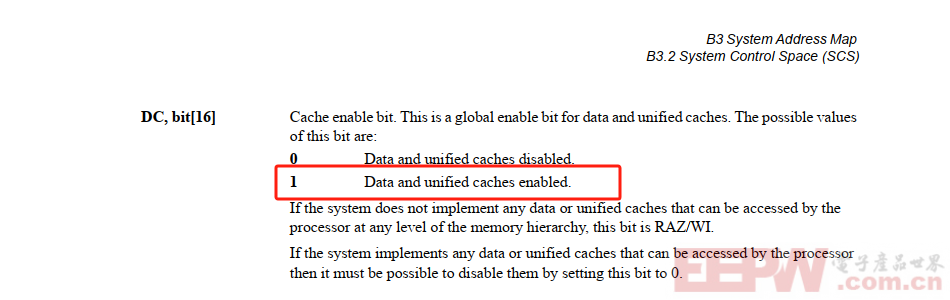

以下代码使能cache

S32_SCB->CCR |= (uint32)SCB_CCR_DC_Msk; /* enable D-Cache */

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

以下是I CACHE 初始化处理,invalidate 后使能ICACHE

#ifdef I_CACHE_ENABLE

/*init Code caches*/

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

S32_SCB->ICIALLU = 0UL; /* invalidate I-Cache */

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

S32_SCB->CCR |= (uint32)SCB_CCR_IC_Msk; /* enable I-Cache */

ASM_KEYWORD("dsb");

ASM_KEYWORD("isb");

#endif /*I_CACHE_ENABLE*/

19

19