人工智能和机器学习应用的爆炸式增长已经将高性能计算系统推向极限。在训练日益复杂的AI模型时,计算需求从2010年的petaFLOPs飙升到今天的yottaFLOPs,预计到2030年将达到quettaFLOPs。这种大规模增长暴露出现代计算架构中的一个关键瓶颈:芯片间数据传输所消耗的能量远远超过计算操作本身。要理解新兴的3D电子-光子互连平台如何解决这一挑战,需要深入研究当前铜基系统的根本限制以及光学技术提供的解决方案[1]。

01互连性能挑战的本质

在评估互连技术时,需要同时考虑多个性能维度。能效衡量传输每比特数据需要多少皮焦耳能量。带宽密度表示给定区域可以流通多少数据,通常以每平方毫米千兆比特每秒来衡量。硅效率指收发器线路消耗多少芯片面积,而链路延迟则反映数据传输的时间延迟。这些指标组合成一个综合性能指标,揭示了不同互连方法在各种链路长度和应用场景下的表现。

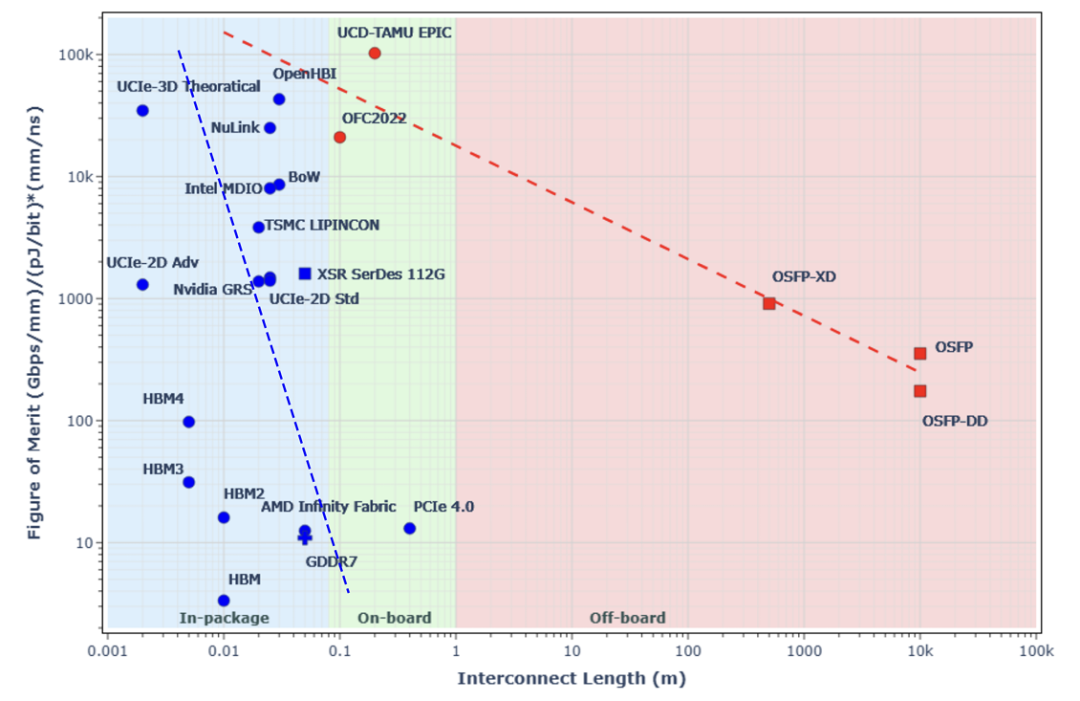

图1:性能对比展示不同互连技术如何随链路长度扩展,光学互连在较长距离保持优异性能,而电气互连仅在极短距离表现出色。

性能格局在不同互连类型中呈现出明显的模式。使用铜传输线的传统电气互连在极短距离(如3D堆叠高带宽存储器模块内的连接)表现良好。然而,当链路长度超过几毫米时,性能会急剧下降。相比之下,光学互连在更长距离上保持稳定的高性能,使其成为封装内芯片到芯片通信及更远距离的理想选择。考虑所有性能因素后,光学方案变得更优的交叉点出现在出乎意料的短距离处。

02铜与光的基础物理学

要理解光学互连的优势,必须了解铜互连的物理限制。当高速电信号通过铜传输线传播时,会经历多种形式的衰减。导电损耗发生在电子遇到金属电阻时。介电损耗源于导体周围的绝缘材料。相邻信号线之间的串扰会产生干扰并破坏数据。色散导致信号的不同频率分量以不同速度传播,使数字脉冲展宽并造成时序错误。这些损伤都会随频率和距离的增加而恶化,迫使设计者添加复杂且耗能的数字信号处理线路。

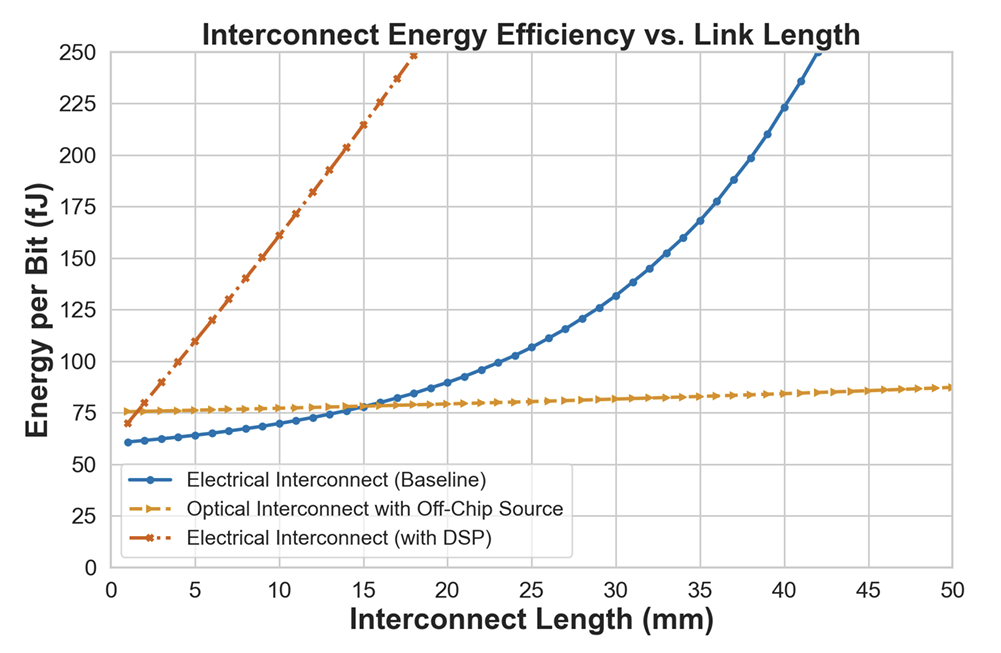

图2:能效对比揭示了光学互连比电气互连更节能的分界长度,在此分析中仅为15.1毫米。

考虑在8 Gbps数据速率下的实际对比。铜互连在极短链路中消耗相对适中的能量,但每比特能量随距离呈指数增长。光学互连则保持几乎恒定的能耗,与长度无关。对于这种配置,称为分界长度的临界转换点出现在约15毫米处。当考虑到铜链路需要用于均衡、纠错和时钟恢复的数字信号处理线路时,分界长度急剧缩短至仅2.5毫米。这些线路每比特可消耗20到1900飞焦耳,对电气系统构成显著的能量负担。

033D电子-光子架构

提出的解决方案涉及通过光学硅通孔(TSOV)垂直穿过堆栈,将多个chiplet以3D方式堆叠并用光学互连连接。这种架构从根本上改变了对芯片间通信的思考方式。高速连接不再局限于可放置铜凸块的芯片边缘,光信号可以从芯片区域的任何位置发出。堆栈中的每个chiplet都可以与同一堆栈或不同堆栈中的任何其他chiplet直接通信,创建真正的全局互连fabric。

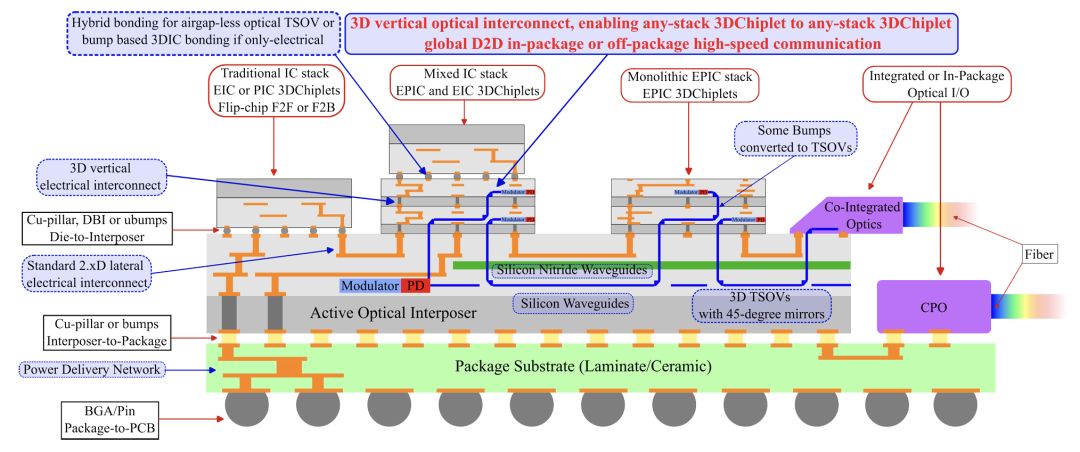

图3:3D chiplet堆叠平台的架构概览,展示光学TSOV如何实现垂直通信,而传统电气TSV处理功率传输和低延迟控制信号。

该平台巧妙地结合了电气和光学领域的优势。传统的硅通孔和2.5D互连继续处理功率传输以及短距离、延迟敏感的通信,如缓存一致性内存访问。光学层接管所有高带宽、长距离的数据移动。这种混合方法保持了与现有标准(如高带宽内存接口)的向后兼容性,同时通过波分复用实现带宽密度的大幅提升。

04通过波长复用扩展带宽密度

当研究波分复用如何扩展容量时,这种光学方法的带宽优势变得显著。通过将一小部分电气凸块转换为光学TSOV,然后在每个TSOV中复用多个波长通道,系统实现了电气互连无法达到的带宽密度。从每个TSOV仅4个波长通道开始就能提供有竞争力的性能,但扩展到32或64个通道可实现超过每平方毫米10太比特每秒的带宽密度。

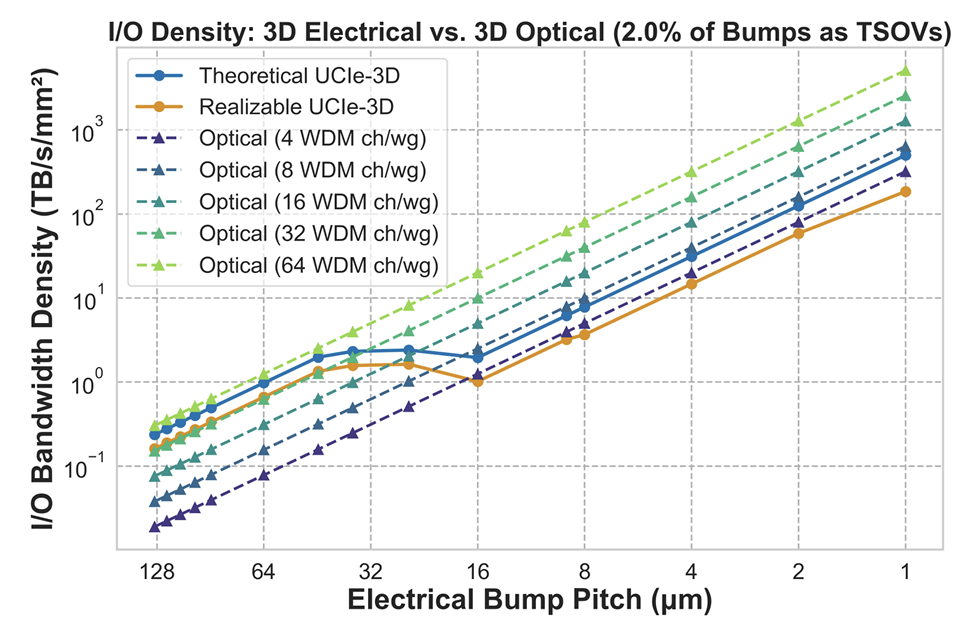

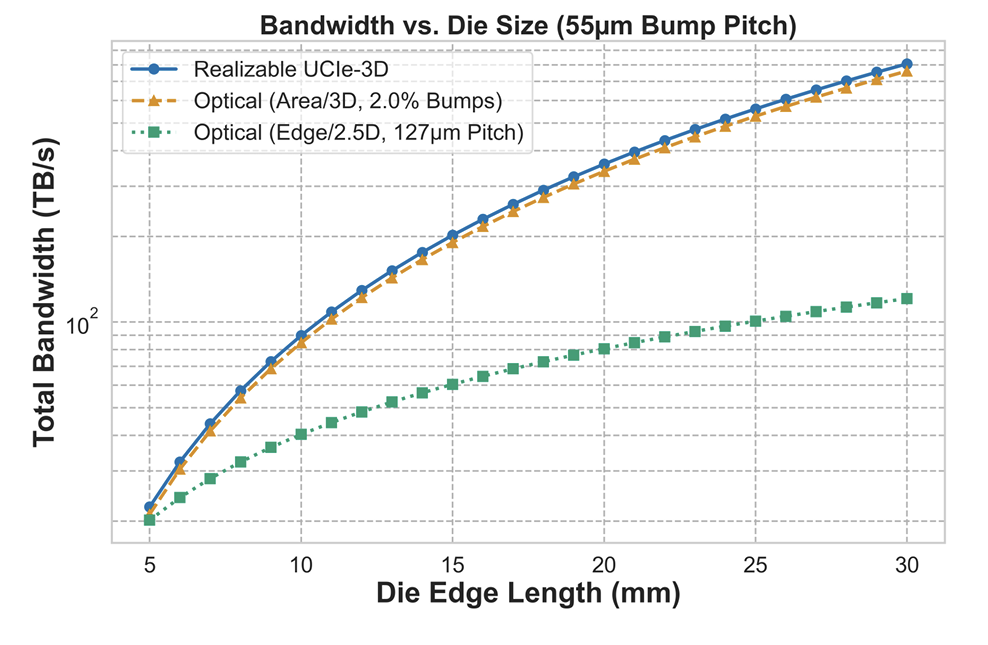

图4:带宽密度对比显示具有不同波长数的3D光学互连在各种凸块间距范围内超越电气互连。

扩展数学对光学系统有利,因为基于面积的互连随芯片边长的平方扩展,而基于周边的方法线性扩展。随着芯片尺寸增长到30毫米边长及以上,面积分布光学I/O的优势变得压倒性。在55微米间距下,2%的凸块转TSOV转换率可以匹配甚至超过最密集电气互连的总带宽,同时在更宽松的电气互连密度下运行,简化了功率传输网络设计。

图5:总带宽随芯片尺寸的扩展,说明基于面积的3D光学互连相对于基于周边的2.5D光学方法的平方优势。

05使能技术与实现路径

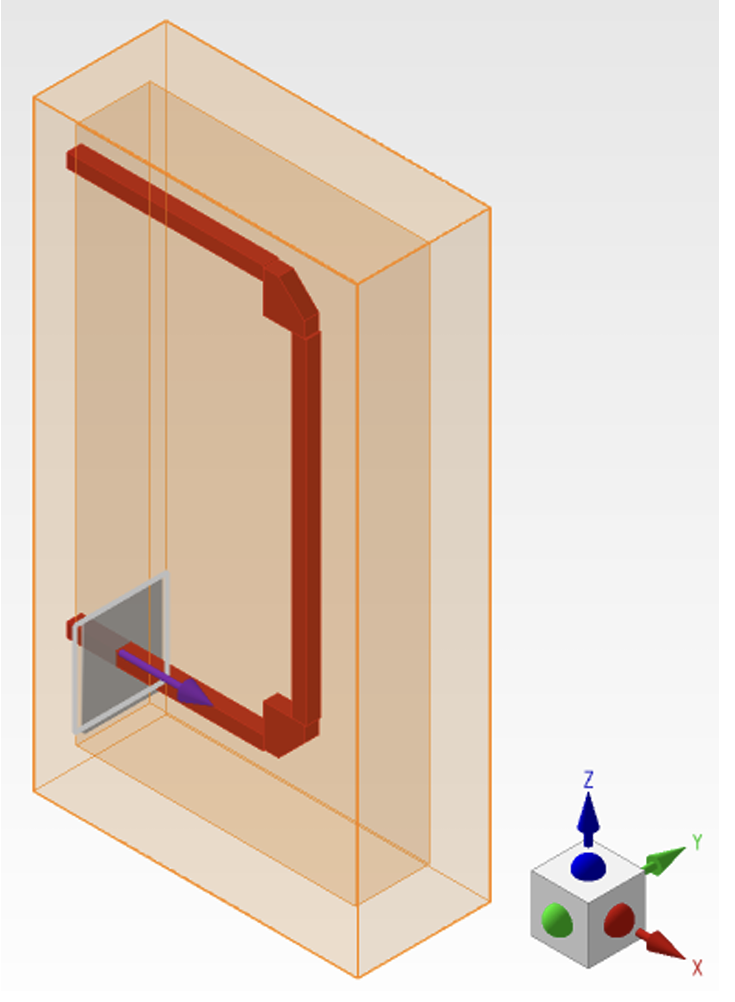

实现这一愿景需要几项关键的使能技术。光学硅通孔代表了最核心的创新。这种结构使用45度镜面将光从水平波导重定向到穿过硅基板的垂直波导中。仿真显示在通信C波段的耦合损耗低于1分贝,优化设计可实现低至0.42分贝。使用Bosch刻蚀的制造已成功生产出20微米高、纵横比为54:1的通孔,开发目标是100微米高度,纵横比超过270:1。

图6:TSOV结构的详细FDTD仿真模型,显示45度镜面部分和垂直波导每次转换的损耗小于1分贝。

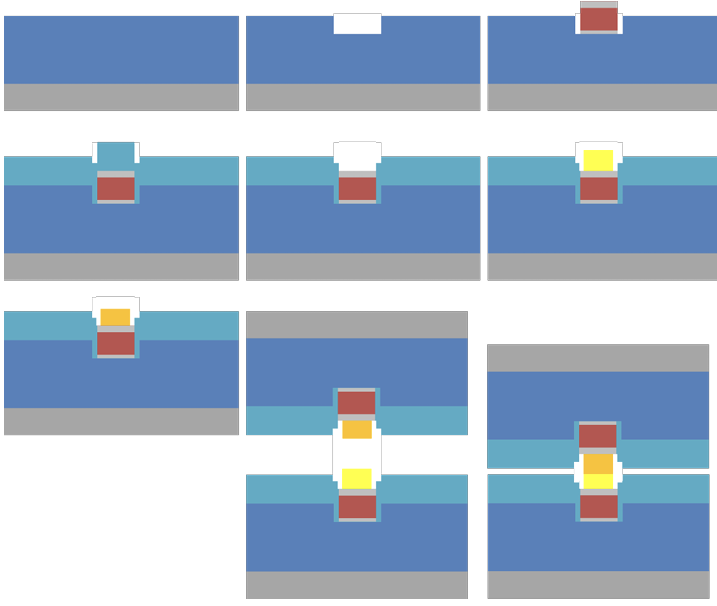

电子和光电子芯片chiplet的集成需要先进的键合技术。金锡共晶键合为最终实现无气隙键合提供了路径,这对TSOV的最佳对准是必需的。这种方法相比传统焊料凸块键合的优势在于能够进行多级assembly而无回流风险。目前的开发已实现超过22千克力的键合强度,芯片断裂发生在键合断裂之前,展示了稳固的机械连接。

图7:分步键合工艺开发,展示共晶冶金方法,实现可靠的芯片对芯片集成,无需面对与气隙相关的对准挑战。

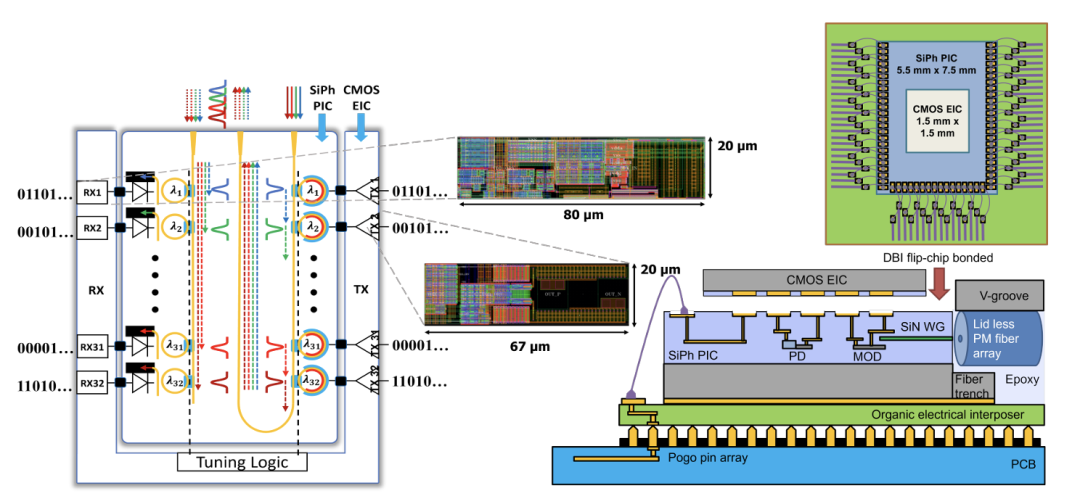

光电子芯片和电子线路之间的寄生电容对接收器灵敏度和整体系统能效起决定性作用。直接键合互连技术将互连电容降低至仅7.2飞法,而传统C4凸块为31.6飞法。这种降低使得在25 Gbps下实现了创纪录的负17.01分贝光调制幅度接收器灵敏度,能效达到191飞焦耳每比特。未来的单片集成可将总输入电容降至3.2飞法,将灵敏度再提高8.36分贝,为最终目标100飞焦耳每比特或更低提供了清晰的路径。

图8:3D异构收发器完整系统架构,显示共同设计的电子和光电子集成芯片以及使用波分复用的32个光学通道。

光学路由、先进键合和异构集成方面的这些创新融合,创建了一个解决未来高性能计算可扩展性所有主要限制的平台,在带宽和密度方面实现节能通信。

我要赚赏金

我要赚赏金