在这一小节中,我们主要介绍ARMv8架构中AArch64执行状态下的寄存器使用情况。ARM架构中的寄存器主要有两类,一类用于提供系统控制与状态报告;另一类用于指令运行和异常处理。我们主要讨论第二类。

通用寄存器主要用于基本指令集中的指令运行,通用寄存器共有31个,编号为R

通用寄存器主要用于基本指令集中的指令运行,通用寄存器共有31个,编号为R0-R31。这些通用寄存器可以被当成31个64bit的寄存器,编号为X0-X30;或者被作为31个32bit的寄存器,编号为W0-W30。

在AArch64执行状态下,除了通用寄存器外,每一个异常级别都会有一个栈指针寄存器(StackPointer Register, SP),栈指针寄存器为SPEL0和SPEL1。异常级别用于区分指令的执行权限,我们将在本章的第四期介绍。如果处理器实现中包含EL2,那么还有SPEL2。如果处理器实现中包含EL3,那么还有SPEL3。详情可参考链接[5]。

SIMD和浮点寄存器共用一系列寄存器,这些寄存器会用于浮点操作、向量操作和其它SIMD有关的标量操作。SIMD指令是能够复制多个操作数、并把它们打包在大型寄存器的一组指令集[3]。以加法指令为例,单指令单数据(SISD)的CPU对加法指令译码后,执行部件先访问内存,取得第一个操作数;之后再一次访问内存,取得第二个操作数;随后才能进行求和运算。而在SIMD型的CPU中,指令译码后几个执行部件同时访问内存,一次性获得所有操作数进行运算。浮点寄存器和SIMD寄存器共包含32个128bit位宽的寄存器,V0-V31。这些寄存器可以作为:

·

32个双字(64bit)寄存器,D0-D31。

·

·

32个单字(32bit)寄存器,S0-S31。

·

·

32个半字(16bit)寄存器,H0-H31。

·

·

32个单字(8bit)寄存器,B0-B31。

·

程序状态寄存器(Current Program Status Register,CPSR) 在用户级编程时用于存储条件码。CPSR包含条件码标志,中断禁止位,当前处理器模式以及其他状态和控制信息。

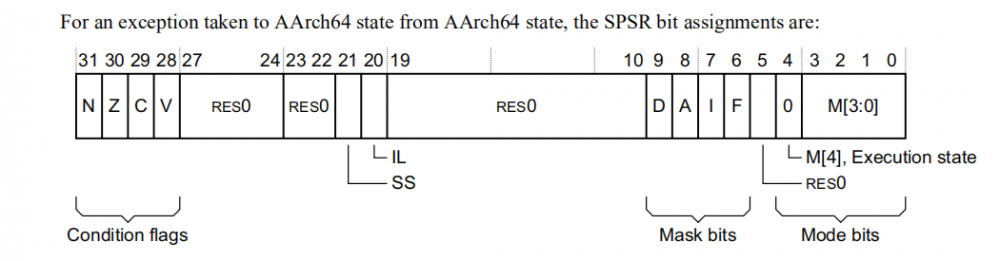

保存程序状态寄存器(SPSR,Saved Program StatusRegister)用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。在A64中,不再使用单一的CPSR寄存器,来保存当前处理器状态,而是用PSTATE来保存处理器状态,而在A32中依然使用CPSR。有关PSTATE和CPSR的详细信息可参考链接[4]。A64中SPSR 格式的示意图如下图所示:

其中N、Z、C、V均为条件码标志位。它们的内容可被算术或逻辑运算的结果所改变,并且可以用于决定某条指令是否被执行,其含义如下表所示[8]:

标志位 | 含义 |

N | 当两个有符号整数运算时:N=1表示运算的结果为负数;N=0表示运算的结果为正数或零。 |

Z | Z=1表示运算的结果为零,Z=0表示运算的结果非零。 |

C | 可以有4种方法设置C的值: · 在加法指令中(包括比较指令CMP),当结果产生了进位,则C=1,表示无符号运算发生上溢出;其他情况C=0。 · · 在减法指令中(包括减法指令CMP),当运算中发生借位,则C=0,表示无符号运算数发生下溢出;其他情况下C=1。 · · 对于包含移位操作的非加减运算指令,C中包含最后一次溢出的位的数值。 · · 对于其他非加减运算指令,C位的值通常不受影响。 · |

V | 对于加减运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号为溢出,通常其他指令不影响V位。 |

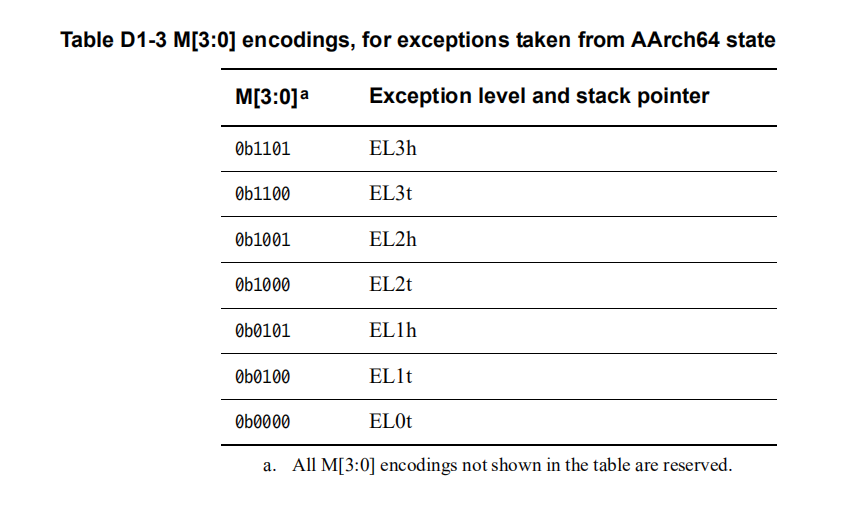

M[3:0]则用来确定异常级别和SP:

有关SPSR中各个位的详细信息可以参考文献[1] 1.6.4小节。

连接寄存器LR(R14)的主要作用有两个:

1. 保存子程序返回地址,用MOVE指令或BX指令可以用于实现返回,如MOV PC、LR或BXLR。若子程序中还需要调用子程序,则可以写为:

第一条指令将LR中的内容入栈,最后一条将栈中保存的LR寄存器的内容存入PC中用于返回。

2. 当异常发生时,异常模式的LR用于保存异常返回地址,将LR内容入栈可以处理嵌套中断。

PC是程序计数器,其中保存的是正在被加载的指令,而不是正在被执行的指令。例如,若指令长度为4byte,则PC指向当前正在被执行的指令的地址+8byte的地址。关于LR和PC的详细内容可参考文献[6]和[7]。

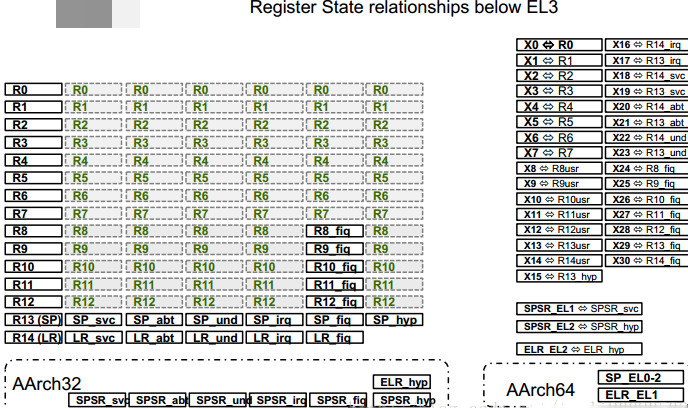

以下是异常级别EL3中使用的寄存器的例图:

ARM架构中处理器有不同的运行模式,因此同一个功能的寄存器在不同的运行模式下可能对应不同的物理寄存器,这些寄存器被称为备份寄存器。如SPSR_svc表示svc模式下使用的SPSR寄存器。ARM架构中常用的运行模式如下表所示[9]:

处理器模式 | 描述 |

用户模式(User, usr) | 正常程序执行的模式 |

快速中断模式(FIQ, fiq) | 用于高速数据传输和通道处理 |

外部中断模式(IRQ, irq) | 用于通常的中断处理 |

特权模式(Supervisor, svc) | 供操作系统使用的一种保护模式 |

数据访问中止模式(Abort, abt) | 当数据或指令预取中止时进入该模式,用于虚拟存储及存储保护 |

未定义指令中止模式(Undefined, und) | 当执行未定义指令时进入该模式,用于支持通过软件仿真硬件的协处理器 |

系统模式(System, sys) | 用于运行特权级的操作系统任务 |

ARMv8-A架构还有Monitor(mon)工作模式,用于处理器安全状态与非安全状态的切换,Hypervisor(hyp)模式则用于对虚拟化有关功能的支持。有关安全状态的详细内容在后续的文章中会介绍。

我要赚赏金

我要赚赏金