继续学习VerilogHDL。

大致浏览了下VerilogHDL程序设计与实践,整个书看得也是云里雾里的。前几天看51FPGA版主的教程遇见的几个问题重点看了下。

有点小收获。今天刚把ModelSIM装上去了,这不晚上就来显摆了。

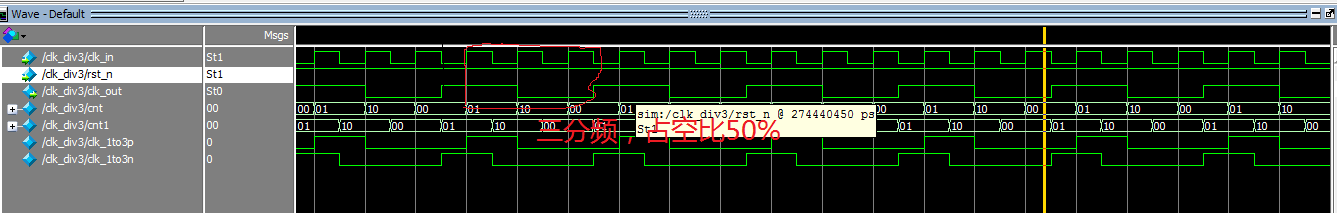

实验是哟个三分频器,占空比是50%的三分频器。参照书上的做法,用一个占空比为1/3 和一个占空比为2/3的波形进行或运算,之后就得到了占空比为占空比为50%的波形,当然这两个进行与运算的波形相位是一致的。

先看RTL级的框图,我是没看明白为什么会这样,但各个模块很清晰

再上波形图,ModelSim10d里边进行的仿真。

最后是代码:

/*3分频器 占空比50%*/

module clk_div3(clk_in,rst_n,clk_out);

input clk_in;

input rst_n;

output clk_out;

reg [1:0] cnt,cnt1;

reg clk_1to3p,clk_1to3n;

always@(posedge clk_in) //两个Always块并行执行,

begin

if(!rst_n) //复位时候的处理

begin

cnt<=0;

clk_1to3p <= 0;

end

else

begin

if(cnt == 2'b10)

begin

cnt<=0; //数数,到2就归零。波形不反转

clk_1to3p <= clk_1to3p;

end

else

begin

cnt <= cnt+1; //数数,0和1时候波形反转。

clk_1to3p <= !clk_1to3p;

end

end

end

always@(negedge clk_in)

begin

if(!rst_n)

begin

cnt1<=0;

clk_1to3n <=0;

end

else

begin

if(cnt1 == 2'b10)

begin

cnt1<=0;

clk_1to3n <=clk_1to3n;

end

else

begin

cnt1<= cnt1+1;

clk_1to3n <=!clk_1to3n;

end

end

end

assign clk_out = clk_1to3p | clk_1to3n; //或运算,得到占空比50%的波形

endmodule

我要赚赏金

我要赚赏金