依然是一个模拟实验,led输出反转表示led闪烁

代码基本没动,只是仿真时候如果分频太高的话不容易看出来led端的波形,将分频比降低到了32分频。

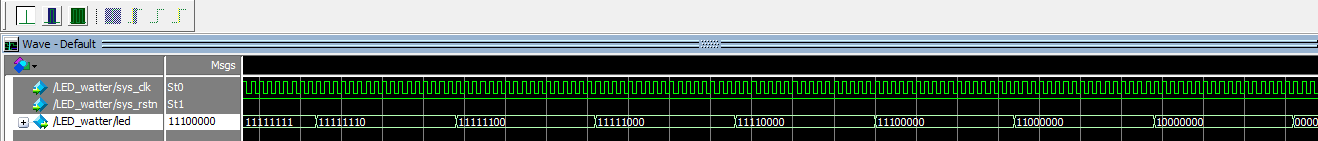

仿真时,将sys_clk设置为时钟。先将sys_rstn强制设置为0,运行一下停止后再将其设置为1.即先复位一下,才能是led开始工作

设置时钟:

设置复位信号:

仿真时实验结果如图:

程序代码如下,要注意两个啊always模块是并行执行的与c语言有区别:

module LED_Flicker(sys_clk,sys_rstn,led);

//变量定义

input sys_clk;

input sys_rstn;

output [7:0] led;

//定义寄存器

reg [7:0] led;

reg [5:0] delay_cnt;

//两个always模块并行执行

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

delay_cnt <= 5'd0;

end

else

begin

if(delay_cnt == 5'd16)

delay_cnt <= 5'd0;

else

delay_cnt <= delay_cnt+1'b1;

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

led <= 8'b11111111;

else

if(delay_cnt == 5'd16)

led <=~led;

else

led <= led;

end

endmodule

我要赚赏金

我要赚赏金