常见术语解释VCC:C=circuit 表示电路的意思, 即接入电路的电压;

VDD:D=device 表示器件的意思, 即器件内部的工作电压;

VSS:S=series 表示公共连接的意思,通常指电路公共接地端电压。

VDDQ&&VSSQ: Q=quality,代表质量好的意思。VDDQ就是高质量的VDD。因为它要经过滤波的,电源质量要比一般的VDD好。同样可以理解VSSQ的含义。

说明1、对于数字电路来说,VCC是电路的供电电压,VDD是芯片的工作电压(通常Vcc>Vdd),VSS是接地点。

2、有些IC既有VDD引脚又有VCC引脚,说明这种器件自身带有电压转换功能。

3、在场效应管(或COMS器件)中,VDD为漏极,VSS为源极,VDD和VSS指的是元件引脚,而不表示供电电压。

4、一般来说VCC=模拟电源,VDD=数字电源,VSS=数字地,VEE=负电源

电路中的解释:

单解: VDD:电源电压(单极器件);电源电压(4000系列数字电路);漏极电压(场效应管)

VCC:电源电压(双极器件);电源电压(74系列数字电路);声控载波(Voice Controlled Carrier)

VSS::地或电源负极

VEE:负电压供电;场效应管的源极(S)

VPP:编程/擦除电压。

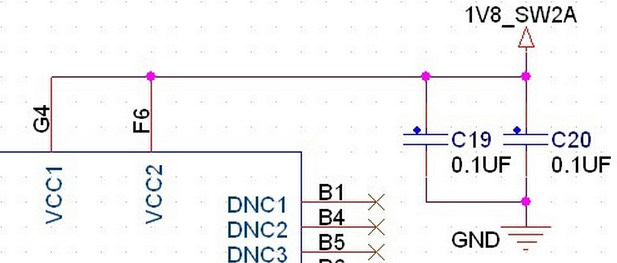

芯片电源电路分析:下图1为NAND FLASH VCC端的电源电路:

图1 NAND FLASH 电源端电路

电路分析:

图中的两个0.1UF的电容C19、C20为无极性去耦电容,去耦电容一般连接电源和地,而且是紧紧靠近电路的电源接入点,是用于滤除该部分电路因内部器件频繁开关对外部产生的传导干扰;特别数字电路,几乎所有的器件都处在高频的时序电平切换状态,于是对电源的产生频率很高的忽高忽低的电流需求,这样电流就形成了传导的脉冲干扰,对其他数字器件可能产生误动作,严重影响电路的正常工作,所以一般的数字IC,在电源的引脚旁,一般都有个0.1uF的去耦电容。0.1μF的去耦电容有5μH的分布电感,它的谐振频率大约在7MHz左右,也就是说,对于 10MHz以下的噪声有较好的去耦效果。去耦电容的选用并不严格,可按C=1/F,即10MHz取0.1μF,100MHz取0.01μF。

另外,去耦电容的个数与VCC线数有关,每个VCC电源引脚都需要加一个去耦电容。上图是原理图的去耦电容的画法,在PCB设计中,每个去耦电容都要接到相应的VCC引脚下。

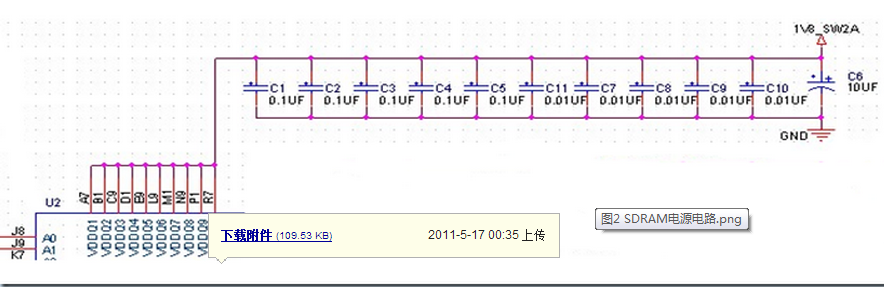

图2为SDRAM 电源引脚VDDQ端的电路:

图中C1-C10电容为去耦电容,分别对应引脚VDDQ1-VDDQ10,电容容值不同是由于芯片不同的部分工作的频率不同。每10片左右集成电路要加一片充放电电容,或1个蓄能电容,可选10μF左右,如图中的C6电容。

在BYPASS电路中有两种好方法;

(1)双通道:大电容与小电容(0.1-0.01UF)。

(2)多通道:相同的小电容并联(一般是NF级的电容)

本电路采用的是双通道法。

电源中高频干扰是典型的无用成分,需要将其在进入目标芯片之前提前干掉,一般我们采用电容到达该目的。用于该目的的电容就是所谓的旁路电容(Bypass Capacitor),它利用了电容的频率阻抗特性(理想电容的频率特性随频率的升高,阻抗降低),可以看出旁路电容主要针对高频干扰(高是相对的,一般认为20MHz以上为高频干扰,20MHz以下为低频纹波)。在电源电路中,旁路和退耦都是为了减少电源噪声。旁路主要是为了减少电源上的噪声对器件本身的干扰(自我保护);退耦是为了减少器件产生的噪声对电源的干扰(家丑不外扬)。讨论中并不刻意区分退耦和旁路,认为都是为了滤除噪声,而不管该噪声的来源。

大小两个电容并联的原因:0.1UF的电容滤除低频噪声,0.01UF电容滤除高频噪声。

实际工程中采用电容并联的原因:

电容并联

理论上我们两个电容并联的容值是他们的和,但是在实际应用中,我看到有人把不同容值的两个磁片电容并联使用,想让容值大的虑掉低频,容值小的虑高频。我们在做板子的电源插口的时候也是这么做的,用100uF的极性电容在并联一个0.1uF的电容。理由是,实际的电容可以看成是由电阻,电感和电容串连的。

大容量的电容器一般是用长条型极板卷绕而成,这就不开避免的存在电感和电阻。电感使高频性能变差,电阻使容抗增大,所以在高性能的电源中往往使用多个不同容量的极性电容和无极性电容并联。

一般没有什么要求如精度、容抗等的电路没有必要采用容值相同的电容并联,如果现有电容器容量达不到线路要求可以采用并联方式,其效果只是增大电容器的容量。如果电路中有精度要求,可以采用并联方式提高精度,比如需要一只0.2uF的电容器,一般产品接近的为0.22uF,则可以采用两只0.1uF的电容并联而成。在有容抗要求的电路中,可以采用容值相同的电容器并联来降低容抗。

为什么大电容并联一个小电容?

理想的电容,其阻抗随频率升高而变小(R=1/jwc), 但理想的电容是不存在的,由于电容引脚的分布电感效应,在高频段电容不再是一个单纯的电容,更应该把它看成一个电容和电感的串联高频等效电路,当频率高于其谐振频率时,阻抗表现出随频率升高而升高的特性,就是电感特性,这时电容就好比一个电感了。

相反电感也有同样的特性。

大电容并联小电容在电源滤波中非常广泛的用到,根本原因就在于电容的自谐振特性。大小电容搭配可以很好的抑制低频到高频的电源干扰信号,小电容滤高频(自谐振频率高),大电容滤低频(自谐振频率低),两者互为补充,而且电容并联好处多多,电感越并越小,并且小容量电容的电感要大大低于大容量电容的电感。

“大小电容搭配可以很好的抑制低频到高频的电源干扰信号,小电容滤高频(自谐振频率高),

大电容滤低频(自谐振频率低),两者互为补充。 ”

大并小处理比较困难,高中低不容易得到平衡,容量差的越大越明显。实在要并的话,最好以10倍的数量级依次递减,比如10000u+1000u+100u+10u(0.1u)。尤其耦合电容,大并小影响最大。耦合电容建议同容量相同的电容并联。

转载:http://bbs.21ic.com/icview-236292-1-1.html

我要赚赏金

我要赚赏金