ADC0809是8路8位逐次逼近型A/D转换CMOS器件,在过程控制和机床控制等应用中,能对多路模拟信号进行分时采集和A/D转换,输出数字信号通过三态缓冲器,可直接与微处理器的数据总线相连接。

一:ADC0809的内部结构和引脚共能

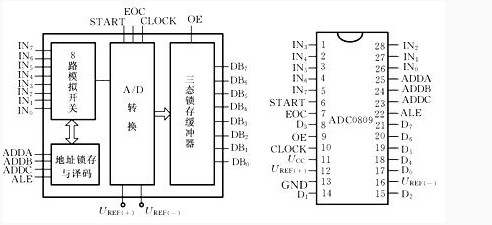

ADC0809的内部结构原理如图10.3.1所示,芯片的主要组成部分是一个8位逐次比较型A/D转换器。为了实现8路模拟信号的分时采集,片内设置了带有锁存功能的8路模拟选通开关,以及相应的通道地址锁存和译码电路,可对8路0~5V的输入模拟电压进行分时转换,转换后的数据送入三态输出数据锁存器。ADC0809的主要特性如下:

(1) 辨率为8位

(2) 最大不可调误差小于正负ULSB

(3) 可锁存三态输出,能与8位微处理器接口

(4) 输出与TTL兼容

(5) 不必进行零点和满度调整

(6) 单电源供电,供电电压为+5V

(7) 转换数率取决于芯片的时钟频率,时钟频率范围是:10~1280KHZ。当时钟频率选为500KHZ时,对应的转换时间为128us.

ADC0809的芯片的引脚如图10.3.2所示,引脚功能说明如下:

IN0~IN7:8路模拟信号输入端

D0~D7:8位数字量输出端

START:启动控制输入端,高电平有效,用于启动ADC0809内部的A/D转换过程

ALE:地址锁存控制输入端。ALE端可与START端连接在一起。通过软件输入一个正脉冲,可立即启动A/D转换

EOC:转换结束信号输出端。开始A/D转换时为低电平,转换结束是输出高电平

OE:输出允许控制端,用于打开三态输出锁存器。当OE为高电平时,打开三态数据输出锁存器,将转换后的数据凉输送到数据总线上

CLK:始终信号输入端

ADDA(ADDB、ADDC):8路模拟选通开关的3位地址选通输入端;其地址码与输入通路的对应关系如表10.3.2所示

VCC:供电电源输入端

VREF(+):参考电压正端

VREF(-):参考电压负端

GND:地

我要赚赏金

我要赚赏金