1,既然UART可以打印出信息来,那我们可以打印内存中的值。在506行添加如下代码:

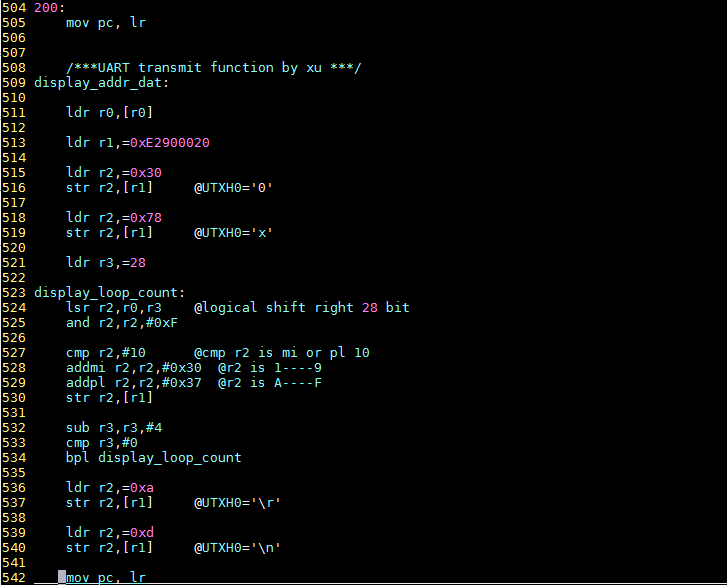

1 2 /***UART transmit function by xu ***/ 3 display_addr_dat: 4 5 ldr r0,[r0] 6 7 ldr r1,=0xE2900020 8 9 ldr r2,=0x3010 str r2,[r1] @UTXH0='0'11 12 ldr r2,=0x7813 str r2,[r1] @UTXH0='x'14 15 ldr r3,=2816 17 display_loop_count:18 lsr r2,r0,r3 @logical shift right 28 bit 19 and r2,r2,#0xF 20 21 cmp r2,#10 @cmp r2 is mi or pl 10 22 addmi r2,r2,#0x30 @r2 is 1----9 23 addpl r2,r2,#0x37 @r2 is A----F24 str r2,[r1]25 26 sub r3,r3,#427 cmp r3,#028 bpl display_loop_count29 30 ldr r2,=0xa31 str r2,[r1] @UTXH0='\r'32 33 ldr r2,=0xd 34 str r2,[r1] @UTXH0='\n'35 36 mov pc, lr

如图:

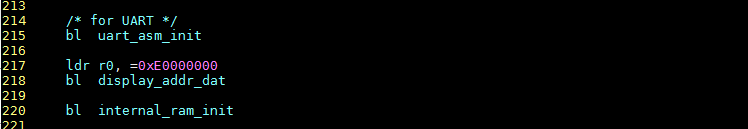

2,这样我们可以进行测试,在216行,进行添加执行代码,如图:

我们通过手册查询可以得知内存地址oxE000_0000的值为0x43110020。那么重新编译和烧写一下u-boot.bin,看看串口输

出的信息与我们查询的值是否相同。

3,接一下来,我们来自己编写板子的内存初始化代码,可以根据厂家的光盘中裸机代码/src/cdram/memory.S中的代码做相应的

更改。代码如下:

1 /*** ddrmem initialze by xu***/ 2 .globl ddrmem_init 3 ddrmem_init: 4 5 #define ELFIN_GPIO_BASE 0xE0200000 6 #define APB_DMC_0_BASE 0xF0000000 7 #define DMC_CONCONTROL 0x00 8 #define DMC_MEMCONTROL 0x04 9 #define DMC_MEMCONFIG0 0x08 10 #define DMC_DIRECTCMD 0x10 11 #define DMC_PRECHCONFIG 0x14 12 #define DMC_PHYCONTROL0 0x18 13 #define DMC_PHYCONTROL1 0x1C 14 #define DMC_RESERVED 0x20 15 #define DMC_PWRDNCONFIG 0x28 16 #define DMC_TIMINGAREF 0x30 17 #define DMC_TIMINGROW 0x34 18 #define DMC_TIMINGDATA 0x38 19 #define DMC_TIMINGPOWER 0x3C 20 #define DMC_PHYSTATUS 0x40 21 #define DMC_CHIP0STATUS 0x48 22 #define DMC_AREFSTATUS 0x50 23 #define DMC_MRSTATUS 0x54 24 #define DMC_PHYTEST0 0x58 25 //初始化PHY DLL 26 ldr r0, =APB_DMC_0_BASE 27 //step 2 set PhyControl0.ctrl_start_point PhyControl0.ctrl_inc PhyControl0.ctrl_dll_on bit field to 1 28 ldr r1, =0x0010100A 29 str r1, [r0,#DMC_PHYCONTROL0] 30 31 //step 3 set PhyControl1.ctrl_shiftc PhyControl1.ctrl_ctrl_offsetc 32 ldr r1, =0x00000086 33 str r1, [r0,#DMC_PHYCONTROL1] 34 35 //step 4 set PhyControl0.ctrl_start bit-field to 1 DLL on 36 ldr r1, =0x0010100B 37 str r1, [r0,#DMC_PHYCONTROL0] 38 39 find_lock_val: 40 //step 11 loop until DLL is locked 41 ldr r1, [r0,#DMC_PHYSTATUS] 42 and r2, r1,#0x7 43 cmp r2, #0x7 44 bne find_lock_val 45 46 //setp 12 Force value looking 47 and r1, #0x3fc0 48 mov r2, r1, LSL #18 49 orr r2, r2, #0x100000 50 orr r2, r2, #0x1000 51 orr r1, r2, #0xB 52 str r1, [r0,#DMC_PHYCONTROL0] 53 54 //初始化DMC0 55 //step 5 set ConControl 56 ldr r1, =0x0FFF1010 57 str r1, [r0,#DMC_CONCONTROL] 58 59 //step 6 set MemControl 60 ldr r1, =0x00202400 61 str r1, [r0,#DMC_MEMCONTROL] 62 63 //step 7 set MemConfig0 512M config,8 banks 64 ldr r1, =0x20E00323 65 str r1, [r0,#DMC_MEMCONFIG0] 66 67 //step 8/1 set PrechConfig 68 ldr r1, =0xFF000000 69 str r1, [r0,#DMC_PRECHCONFIG] 70 71 //step 9/1 set TimingAref t_refi=7.5us * 133MHz=1038(0x40E) 72 ldr r1, =0x0000040E 73 str r1, [r0,#DMC_TIMINGAREF] 74 //step 9/2 set TimingRow tRAS=45ns tRC=60ns tRCD=15ns tRP=15ns tRRD=7.5ns tRFC=127.5ns 75 ldr r1, =0x11122206 76 str r1, [r0,#DMC_TIMINGROW] 77 //step 9/3 set TimingData tWTR=7.5ns tWR=15ns tRTP=7.5ns cl=4 78 ldr r1, =0x12140000 79 str r1, [r0,#DMC_TIMINGDATA] 80 //step 9/4 set TimingPower t_mrd>=tMRD=2nCK t_cke<=tCKE=3nCK t_xp>=tXP=2nCK tXSRD=200ns tFAW=35ns 81 ldr r1, =0x05DC0343 82 str r1, [r0,#DMC_TIMINGPOWER] 83 84 //初始化DDR2 DRAM 85 //step 14 lssue a "NOP" for DirectCmd and hold CKE to high level 86 ldr r1, =0x07000000 87 str r1, [r0,#DMC_DIRECTCMD] 88 89 //step 16 lssue a "PALL" for DirectCmd 90 ldr r1, =0x01000000 91 str r1, [r0,#DMC_DIRECTCMD] 92 93 //step 17 lssue an "EMRS2" for DirectCmd 94 ldr r1, =0x00020000 95 str r1, [r0,#DMC_DIRECTCMD] 96 97 //step 18 lssue an "EMRS3" for DirectCmd 98 ldr r1, =0x00030000 99 str r1, [r0,#DMC_DIRECTCMD]100 101 //step 19 lssue an "EMRS" for DirectCmd and enable DLLs enable DQS102 ldr r1, =0x00010000103 str r1, [r0,#DMC_DIRECTCMD]104 105 //step 20 lssue a "MRS" for DirectCmd and reset DLL106 ldr r1, =0x00000542107 str r1, [r0,#DMC_DIRECTCMD]108 109 //step 21 lssue a "PALL" for DirectCmd110 ldr r1, =0x01000000111 str r1, [r0,#DMC_DIRECTCMD]112 113 //step 22 lssue two "Auto Refresh" for DirectCmd114 ldr r1, =0x05000000115 str r1,[r0,#DMC_DIRECTCMD]116 117 ldr r1, =0x05000000118 str r1,[r0,#DMC_DIRECTCMD]119 120 //step 23 lssue a "MRS" for DirectCmd and without reseting DLL121 ldr r1, =0x00000442122 str r1, [r0,#DMC_DIRECTCMD]123 124 //step 25 lssue an "EMRS" for DirectCmd set OCD Calibration Default and exit OCD Calibration125 ldr r1, =0x00010380126 str r1, [r0,#DMC_DIRECTCMD]127 128 ldr r1, =0x00010000129 str r1, [r0,#DMC_DIRECTCMD]130 131 //step 27 set ConControl and turn on "auot refresh"132 ldr r1, =0x0FF01030133 str r1, [r0,#DMC_CONCONTROL]134 135 //step 8/2 set PwrdnConfig136 ldr r1, =0xFFFF00FF137 str r1, [r0,#DMC_PWRDNCONFIG]138 139 //step 28 IF power down modes is required set MemControl140 ldr r1, =0x00202400141 str r1, [r0,#DMC_MEMCONTROL]142 143 //putout URAT char "DDR IS OK!"144 ldr r0, =0xE2900020145 ldr r1, =0x44 @UTH='D'146 str r1, [r0]147 148 ldr r1, =0x44149 str r1, [r0] @UTH='D'150 151 ldr r1, =0x52152 str r1, [r0] @UTH='R'153 154 ldr r1, =0x20 155 str r1, [r0] @UTH=' '156 157 ldr r1, =0x49158 str r1, [r0] @UTH='I'159 160 ldr r1, =0x53161 str r1, [r0] @UTH='S'162 163 ldr r1, =0x20164 str r1, [r0] @UTH=' '165 166 ldr r1, =0x4f167 str r1, [r0] @UTH='O'168 169 ldr r1, =0x4b170 str r1, [r0] @UTH='K'171 172 ldr r1, =0x21173 str r1, [r0] @UTH='!'174 175 ldr r1, =0xa176 str r1, [r0] @UTXH0='\r'177 178 ldr r1, =0xd 179 str r1, [r0] @UTXH0='\n'180 181 mov pc, lr

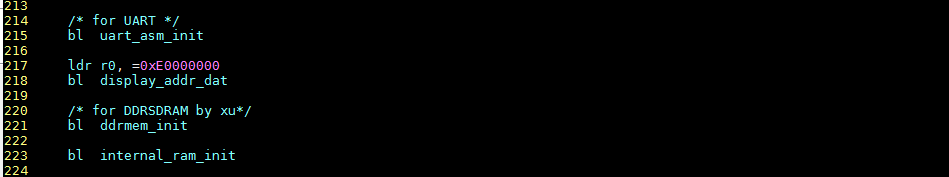

4,在UART执行代码下面添加内存初始化执行代码220-221行。如图:

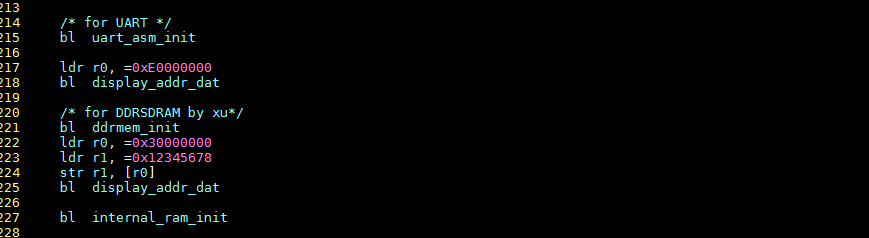

5,内存初始化完成,但是我们不知道内存初始化是否正确,这就需要验证。通过内存读取数据代码来进行验证222行-225行。如图所示:

6,然后,进行make,烧写u-boot.bin.然后可以看到串口输出信息中,输出与我们输入相同的内存地址的值

我要赚赏金

我要赚赏金