系统级芯片 (SoC) 是一种特殊类型的集成电路 (IC) 设计,它将大多数人认为与计算机相关联的典型元件(例如中央处理单元 (CPU)、内存、输入/输出 (IO) 端口和存储器)组合在单个芯片上。SoC 在移动电子行业颇受欢迎,因为与多芯片设计相比,其功耗大大降低,尺寸也小得多。

所有 SoC 都可以分为两个功能区域:内核与 IO 控制。内核执行芯片设计的逻辑。如果传入信号的电压电平高于内核电平,内核失效可能会发生。为了防止发生这种情况,设计人员会使用多种保护结构,这些结构共同形成一个 IO 环。

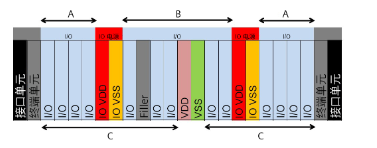

IO 环执行多种功能,其中之一是保护 SoC 的可靠性不受静电放电 (ESD)、闩锁效应、电迁移 (EM) 和 IR 压降等问题的影响。就像任何 IC 一样,准确一致的可靠性验证是 SoC 设计的一项关键要求。但是,SoC 的可靠性验证面临一些独特的挑战。SoC 中使用的知识产权(IP) 通常来自多家专业 IP 供应商。对于 IO 环中的单元布局,每家 IP 供应商都有自己的规则以便用于保护其 IP,如图 1 所示 [1]。此类IO 布局规则基于 IP 设计架构及 IP 供应商的专业知识和经验,不同 IP 供应商的规则通常差异很大。

图 1:IO 环组成部分之间的 ESD 间距规则(来源:ESD Association。许可使用)。

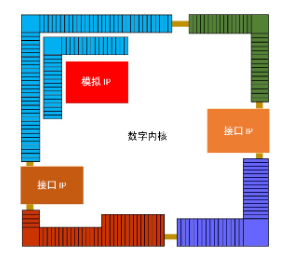

将多个 IP 组合到 SoC 版图中时,SoC 设计人员必须创建一个 SoC IO 环,该环不仅要在整个 SoC 中提供必要的可靠性保护,还要集成这些 IP 的所有不同 IO 环规则,如图 2 所示。如果存在冲突,SoC 设计人员必须与 IP 供应商合作以找到解决方案。

图 2:典型的 IO 环 SoC 设计。

到目前为止,验证这种混合的 IO 环规则通常需要手动检查。众所周知,手动方法不仅耗时,而且容易出现人为错误。另外,此检查是在设计流程后期进行的,当所有 IP 都已整合时,进行更改是非常困难的,而且常常会产生新的错误,导致流片延迟。

在当今复杂的 SoC 中设计和验证 IO 环需要各种有序的步骤,所有这些步骤对于成功完成设计同等重要。现在,通过引入创新的检查功能,再加上支持标准化、可定制 IO 环检查的新接口,SoC 设计人员可以在设计流程的早期满怀信心地识别和纠正 IO 环违规(在此阶段实施纠正和优化要容易得多)。

IO 环检查的新方法

Calibre™ PERC™ 可靠性平台具有创新且独特的能力,可将网表和版图 (GDS) 信息关联起来,因此,自动化 IO 环验证的新选择现已变得切实可行。

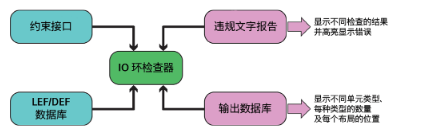

Calibre PERC 可靠性平台将几何和电气约束整合到单次检查中,从而可以分析基于连通性约束的版图限制 [2]。为了支持一致性和易用性,自动化 LEF/DEF IO 环检查框架允许 SoC 设计人员使用众多晶圆代工厂和 IP ESD 布局规则来验证 SoC 的合规性,如图 3 所示。由于能够对 LEF/DEF 设计执行 IO 环验证,因此可以在设计周期中尽早完成此任务,此时最终 signoff 验证尚未开始,仍有机会优化和完善设计 [3]。

图 3:Calibre PERC IO 环检查流程。

……………………

我要赚赏金

我要赚赏金