引言

电荷耦合器件(CCD)作为新兴固体成像器件,具有体积小、重量轻、分辨率高、灵敏度高、可靠性好等优点,广泛应用于图像传感、景物识别、非接触测量等领域。TDI/CCD(时间延时积分、电荷耦合器件),与普通线阵CCD相比,一个主要优点是能够在较低的光照条件下工作;同时,TDI/CCD通过多次曝光可减少像元间响应不均匀和固定图形噪声的影响,提高可见光CCD的灵敏度和均匀性。TDI/CCD在航天航空等领域有着非常广泛的用途。

TDI/CCD应用的关键是驱动信号的产生及输出信号的处理。由于不同厂家不同型号TDI/CCD器件的驱动电路各不相同,致使驱动信号的产生必须根据具体的TDI/CCD器件时序要求来设计驱动电路。如何快速方便地产生TDI/CCD驱动时序,成为TDI/CCD应用的关键。使用专用IC驱动TDI/CCD集成度高但是费用高,灵活性和可移植性不好;传统的时序发生器实现方法如单片机驱动法、EPROM驱动法、直接数字驱动法等,由于速度和功能上的限制,已不能满足TDI/CCD应用向高速、小型化、智能化发展的需要。可编程逻辑器件CPLD以其高集成度、高速度、高可靠性、开发周期短可满足这些需要,与VHDL语言的结合可以很好地解决上述问题。由于可编程逻辑器件可以通过软件编程对其硬件的结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

本文分析了Fairchild公司的时间延时积分线阵电荷耦合器件CCD525芯片的工作过程和对驱动时序的要求,在此基础上设计出合理的时序控制方案。选用复杂可编程逻辑器CPLD作为硬件设计平台,使用VHDL语言对驱动电路方案进行硬件描述,采用QuartusII对所设计的时序发生器成功地进行了系统仿真。

1可选输出CCD驱动时序发生器原理

1.1芯片结构说明

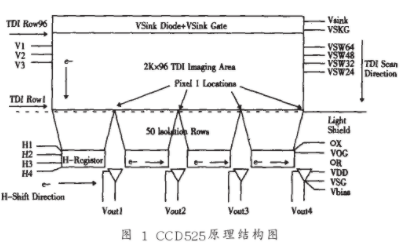

加拿大Fairchild公司的CCD525是一种有效像元数为2048×96的四抽头线阵TDI/CCD,其像敏单元尺寸为13m(水平)×13μm(垂直),TDI级数为24,32,48,64,96可调;每个抽头输出频率为25MHZ,总输出频率为100MHZ。原理结构如图1所示:

它的有效象素单元分四列转移并分别由Vout1、Vout2、Vout3、Vout4三个端口输出;驱动脉冲由垂直转移时钟V1、V2、V3和水平转移时钟H1、H2、H3、H4,复位脉冲(fw),采样脉冲(cy),同步脉冲(tb),钳位脉冲(qw),背景撇出栅脉冲(PIG),积分信号传输到多路传输器控制电极脉冲(PTG)构成。其中钳位脉冲使输出信号钳制在零信号电平上。这些信号均由CCD驱动时序发生器产生。

1.2驱动时序分析

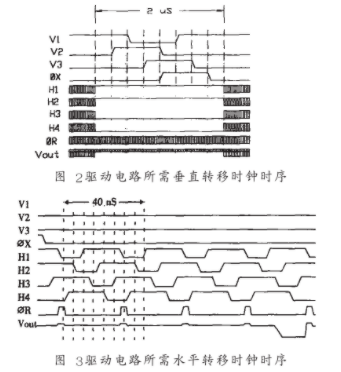

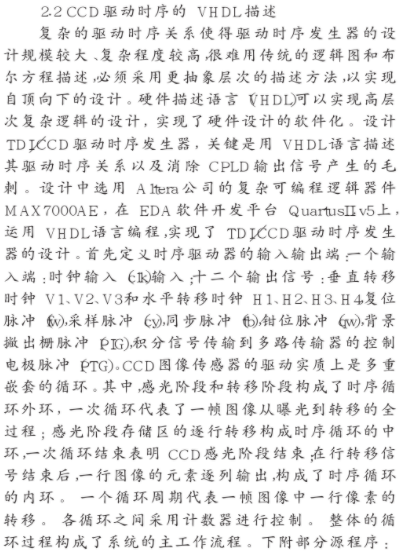

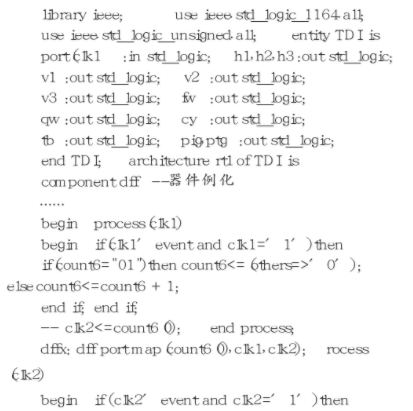

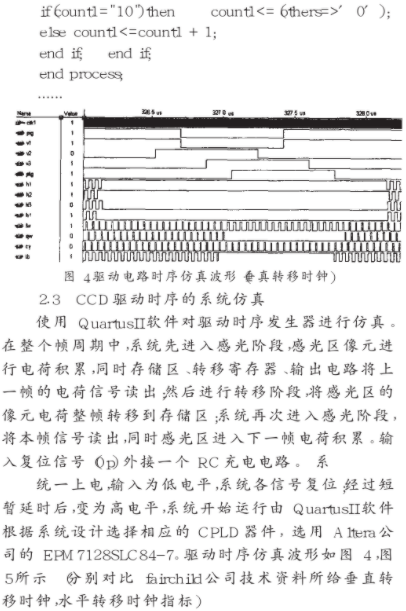

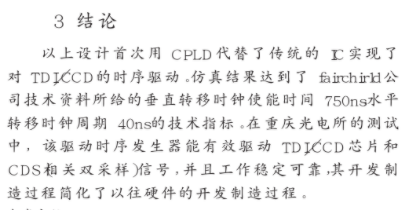

TDI/CCD的一个工作周期分为光积分阶段和电荷转移两个阶段。在光积分阶段,存储栅和模拟移位寄存器隔离,不发生电荷转移,而是分别工作,存储栅进行光积分,采集到的光信号在四相水平驱动脉冲的作用下向四个输出端转移电荷,由Vout1、Vout2、Vout3、Vout4端分别并行输出,复位信号清除移位寄存器中的残余电荷。在电荷转移阶段,存储栅和模拟移位寄存器之间导通,在三相垂直转移脉冲驱动下实现感光阵列光积分所得的光生电荷并行地分别转移到模拟移位寄存器的电荷势阱中。此时,输出脉冲停止工作,输出端没有有效信号输出。以下是CCD525芯片技术资料中提供的所需时序,图2,图3所示:

图3驱动电路所需水平转移时钟时序

进行电荷转移时,三相控制时序依次变化。在整个周期里,CDS(相关双采样)控制信号fw、qw、cy一直有效,占空比较小。由于像元信号噪声的随机性,为了提高了系统信噪比,采用了对像元信号列合并的方式,即每进行两个像元的信号移出(水平转移脉冲信号控制),进行一次复位、钳位、采样,且应对第一个像元复位、钳位,在第二个像元处采样。这样在CDS(相关双采样)的信号存储电容上,将相邻两像元的信号电荷进行积分叠加后输出,实现合并。

2CCD驱动时序的CPLD实现

2.1复杂可编程逻辑器件(CPLD)

引言

电荷耦合器件(CCD)作为新兴固体成像器件,具有体积小、重量轻、分辨率高、灵敏度高、可靠性好等优点,广泛应用于图像传感、景物识别、非接触测量等领域。TDI/CCD(时间延时积分、电荷耦合器件),与普通线阵CCD相比,一个主要优点是能够在较低的光照条件下工作;同时,TDI/CCD通过多次曝光可减少像元间响应不均匀和固定图形噪声的影响,提高可见光CCD的灵敏度和均匀性。TDI/CCD在航天航空等领域有着非常广泛的用途。

TDI/CCD应用的关键是驱动信号的产生及输出信号的处理。由于不同厂家不同型号TDI/CCD器件的驱动电路各不相同,致使驱动信号的产生必须根据具体的TDI/CCD器件时序要求来设计驱动电路。如何快速方便地产生TDI/CCD驱动时序,成为TDI/CCD应用的关键。使用专用IC驱动TDI/CCD集成度高但是费用高,灵活性和可移植性不好;传统的时序发生器实现方法如单片机驱动法、EPROM驱动法、直接数字驱动法等,由于速度和功能上的限制,已不能满足TDI/CCD应用向高速、小型化、智能化发展的需要。可编程逻辑器件CPLD以其高集成度、高速度、高可靠性、开发周期短可满足这些需要,与VHDL语言的结合可以很好地解决上述问题。由于可编程逻辑器件可以通过软件编程对其硬件的结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

本文分析了Fairchild公司的时间延时积分线阵电荷耦合器件CCD525芯片的工作过程和对驱动时序的要求,在此基础上设计出合理的时序控制方案。选用复杂可编程逻辑器CPLD作为硬件设计平台,使用VHDL语言对驱动电路方案进行硬件描述,采用QuartusII对所设计的时序发生器成功地进行了系统仿真。

1可选输出CCD驱动时序发生器原理

1.1芯片结构说明

加拿大Fairchild公司的CCD525是一种有效像元数为2048×96的四抽头线阵TDI/CCD,其像敏单元尺寸为13m(水平)×13μm(垂直),TDI级数为24,32,48,64,96可调;每个抽头输出频率为25MHZ,总输出频率为100MHZ。原理结构如图1所示:

它的有效象素单元分四列转移并分别由Vout1、Vout2、Vout3、Vout4三个端口输出;驱动脉冲由垂直转移时钟V1、V2、V3和水平转移时钟H1、H2、H3、H4,复位脉冲(fw),采样脉冲(cy),同步脉冲(tb),钳位脉冲(qw),背景撇出栅脉冲(PIG),积分信号传输到多路传输器控制电极脉冲(PTG)构成。其中钳位脉冲使输出信号钳制在零信号电平上。这些信号均由CCD驱动时序发生器产生。

1.2驱动时序分析

TDI/CCD的一个工作周期分为光积分阶段和电荷转移两个阶段。在光积分阶段,存储栅和模拟移位寄存器隔离,不发生电荷转移,而是分别工作,存储栅进行光积分,采集到的光信号在四相水平驱动脉冲的作用下向四个输出端转移电荷,由Vout1、Vout2、Vout3、Vout4端分别并行输出,复位信号清除移位寄存器中的残余电荷。在电荷转移阶段,存储栅和模拟移位寄存器之间导通,在三相垂直转移脉冲驱动下实现感光阵列光积分所得的光生电荷并行地分别转移到模拟移位寄存器的电荷势阱中。此时,输出脉冲停止工作,输出端没有有效信号输出。以下是CCD525芯片技术资料中提供的所需时序,图2,图3所示:

图3驱动电路所需水平转移时钟时序

进行电荷转移时,三相控制时序依次变化。在整个周期里,CDS(相关双采样)控制信号fw、qw、cy一直有效,占空比较小。由于像元信号噪声的随机性,为了提高了系统信噪比,采用了对像元信号列合并的方式,即每进行两个像元的信号移出(水平转移脉冲信号控制),进行一次复位、钳位、采样,且应对第一个像元复位、钳位,在第二个像元处采样。这样在CDS(相关双采样)的信号存储电容上,将相邻两像元的信号电荷进行积分叠加后输出,实现合并。

2CCD驱动时序的CPLD实现

2.1复杂可编程逻辑器件(CPLD)

我要赚赏金

我要赚赏金