STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微控制器系列。Cortex-M3内核是为低功耗和价格敏感的应用而专门设计的,具有突出的能效比和处理速度。通过采用Thumb-2高密度指令集,Cortex-M3内核降低了系统存储要求,同时快速的中断处理能够满足控制领域的高实时性要求,使基于该内核设计的STM32系列微控制器能够以更优越的性价比,面向更广泛的应用领域。

STM32系列微控制器为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统设计。STM32系列采用一种新型的存储器扩展技术——FSMC,在外部存储器扩展方面具有独特的优势,可根据系统的应用需要,方便地进行不同类型大容量静态存储器的扩展。

PART2FMSC内部结构

2.1

FSMC技术优势

①支持多种静态存储器类型。STM32通过FSMC可以与SRAM、ROM、PSRAM、NORFlash和NANDFlash存储器的引脚直接相连。

②支持丰富的存储操作方法。FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。

③支持同时扩展多种存储器。FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。

④支持更为广泛的存储器型号。通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。

⑤支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。

2.2

FSMC内部结构

STM32微控制器之所以能够支持NORFlash和NANDFlash这两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NORFlash和NAND/PCCard两个控制器,分别支持两种截然不同的存储器访问方式。在STM32内部,FSMC的一端通过内部高速总线AHB连接到内核Cortex-M3,另一端则是面向扩展存储器的外部总线。

内核对外部存储器的访问信号发送到AHB总线后,经过FSMC转换为符合外部存储器通信规约的信号,送到外部存储器的相应引脚,实现内核与外部存储器之间的数据交互。FSMC起到桥梁作用,既能够进行信号类型的转换,又能够进行信号宽度和时序的调整,屏蔽掉不同存储类型的差异,使之对内核而言没有区别。

2.3

FSMC映射地址空间

FSMC管理1GB的映射地址空间。该空间划分为4个大小为256MB的BANK,每个BANK又划分为4个64MB的子BANK,如表1所列。FSMC中的2个控制器管理的映射地址空间不同。NORFlash控制器管理第1个BANK,NAND/PCCard控制器管理第2~4个BANK。

由于两个控制器管理的存储器类型不同,扩展时应根据选用的存储设备类型确定其映射位置。其中,BANK1的4个子BANK拥有独立的片选线和控制寄存器,可分别扩展一个独立的存储设备,而BANK2~BANK4只有一组控制寄存器。

PART3FSMC扩展外部SRAM配置

3.1

FSMC扩展外部SRAM配置

在STM32与FPGA进行通信的时候,FPGA其实可以看做STM32外部的SRAM。因此相应的配置可以参考对外部SRAM的配置。

SRAM/ROM、NORFlash和PSRAM类型的外部存储器都是由FSMC的NORFlash控制器管理的,扩展方法基本相同,其中NORFlash最为复杂。通过FSMC扩展外部存储器时,除了传统存储器扩展所需要的硬件电路外,还需要进行FSMC初始化配置。

FSMC提供大量、细致的可编程参数,以便能够灵活地进行各种不同类型、不同速度的存储器扩展。外部存储器能否正常工作的关键在于:用户能否根据选用的存储器型号,对配置寄存器进行合理的初始化配置。

3.2

读写时序控制

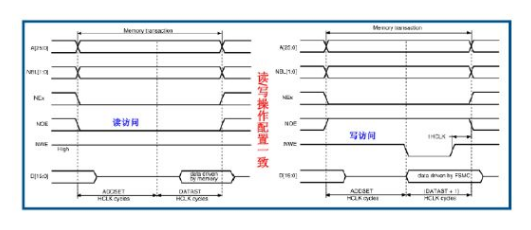

异步通信模式1:SRAM/CRAM

3.3

配置存储器基本特征

通过对FSMC特殊功能寄存器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应控制位的设置,FSMC根据不同存储器特征可灵活地进行工作方式和信号的调整。根据选用的存储器芯片确定需要配置的存储器特征,主要包括以下方面:

①存储器类型(MTYPE)是SRAM/ROM、PSRAM,还是NORFlaSh;

②存储芯片的地址和数据引脚是否复用(MUXEN),FSMC可以直接与AD0~AD15复用的存储器相连,不需要增加外部器件;

③存储芯片的数据线宽度(MWID),FSMC支持8位/16位两种外部数据总线宽度;

④对于NORFlash(PSRAM),是否采用同步突发访问方式(BURSTEN);

⑤对于NORFlash(PSRAM),NWAIT信号的特性说明(WAITEN、WAITCFG、WAITPOL);

⑥对于该存储芯片的读/写操作,是否采用相同的时序参数来确定时序关系(EXTMOD)。

3.4

配置存储器时序参数

FSMC通过使用可编程的存储器时序参数寄存器,拓宽了可选用的外部存储器的速度范围。FSMC的SRAM控制器支持同步和异步突发两种访问方式。

选用同步突发访问方式时,FSMC将HCLK(系统时钟)分频后,发送给外部存储器作为同步时钟信号FSMC_CLK。

此时需要的设置的时间参数有2个:

①HCLK与FSMC_CLK的分频系数(CLKDIV),可以为2~16分频;

②同步突发访问中获得第1个数据所需要的等待延迟(DATLAT)。

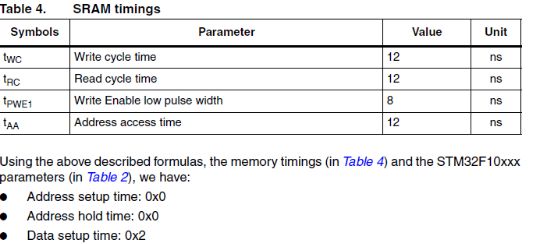

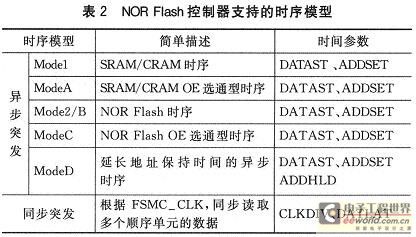

对于异步突发访问方式,FSMC主要设置3个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。FSMC综合了SRAM/ROM、PSRAM和NORFlash产品的信号特点,定义了4种不同的异步时序模型。选用不同的时序模型时,需要设置不同的时序参数,如表2所列。

在实际扩展时,根据选用存储器的特征确定时序模型,从而确定各时间参数与存储器读/写周期参数指标之间的计算关系;利用该计算关系和存储芯片数据手册中给定的参数指标,可计算出FSMC所需要的各时间参数,从而对时间参数寄存器进行合理的配置。

PART4STM32扩展外部SRAM实例

4.1

难点解析

4.1.1数据传输自动化

第一个角度理解STM32有FSMC(其实其他芯片基本都有类似的总线功能),FSMC的好处就是你一旦设置好之后,WR(写)、RD(读)、DB0-DB15这些控制线和数据线,都是FSMC自动控制的。打个比方,当你在程序中写到:

*(volatileunsignedshortint*)(0x60000000)=val;

那么FSMC就会自动执行一个写的操作,其对应的主控芯片的WE、RD这些脚,就会呈现出写的时序出来(即WE=0,RD=1),数据val的值也会通过

DB0-15自动呈现出来(即FSMC-D0:FSMC-D15=val)。地址0x60000000会被呈现在数据线上(即A0-A25=0,地址线的对应最麻烦,要根据具体情况来。

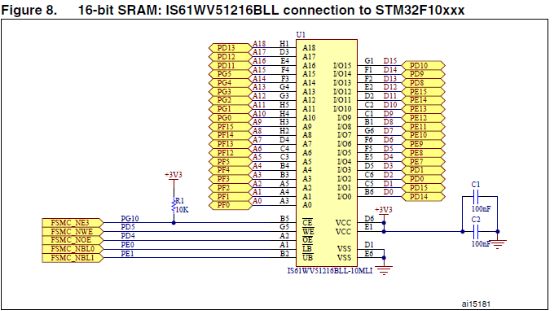

4.1.2硬件连接

硬件平台:(STM32F103VC+EP3C5E144C8N)

将图中的IS61WV512BLL改为FPGA对应的接口即,可按照模式A-SRAM/PSRAM进行连接。

那么在硬件上面,我们需要做的,仅仅是MCU和LCD控制芯片的连接关系:

WE-WR,均为低电平有效

RD-RD,均为低电平有效

FSMC-D0-15接LCDDB0-15

FSMC_NE1--CS接PD7

连接好之后,读写时序都会被FSMC自动完成。但是还有一个很关键的问题,就是RS没有接因为在FSMC里面,根本就没有对应RS。怎么办呢?这个时候,有一个好方法,就是用某一根地址线来接RS。

比如我们选择了A16这根地址线来接,那么当我们要写寄存器(备注:此处应为数据)的时候,我们需要RS,也就是A16(RS为高)置高。软件中怎么做呢?也就是将FSMC要写的地址改成0x60010000,如下:

*(volatileunsignedshortint*)(0x60010000)=val;

这个时候,A16在执行其他FSMC的同时会被拉高,因为A0-A18要呈现出0x60010000。0x60010000里面的Bit17=1,就会导致A16为1。要读数据(备注:此处为寄存器)时,地址由0x60010000改为了0x60000000,这个时候A16就为0了。

RS问题:RS为0表示;读写寄存器;RS为1,读写数据RAM;

4.2

STM32固件对FSMC进行初始化配置

ST公司为用户开发提供了完整、高效的工具和固件库,其中使用C语言编写的固件库提供了覆盖所有标准外设的函数,使用户无需使用汇编操作外设特性,从而提高了程序的可读性和易维护性。

STM32固件库中提供的FSMC的SRAM控制器操作固件,主要包括1个数据结构和3个函数。

FSMC_NORSRAMInitStructure(调用库函数)

RCC_Configuration();(时钟选择)

NVIC_Configuration();(中断优先级)

FSMC_GPIO_Configuration();(连接IO口初始化)

FSMC_SRAM_Init();(FMSC配置)

USART_Initial();(UART1端口配置)

4.3

其他人调试遇到问题点(摘录)

项目中需要使用STM32和FPGA通信,使用的是地址线和数据线,在FPGA中根据STM32的读写模式A的时序完成写入和读取。之前的PCB设计中只使用了8跟数据线和8根地址线,调试过程中没有发现什么问题,在现在的PCB中使用了8根地址线和16根数据线,数据宽度也改成了16位。

刚开始是读取数据不正确,后来发现了问题,STM32在16位数据宽度下有个内外地址映射的问题,只需要把FPGA中的设定的地址乘以2在STM32中访问就可以了,但是在写操作的时候会出现写当前地址的时候把后面的地址写成0的情况,比如说我给FPGA中定义的偏移地址0x01写一个16位数据,按照地址映射,在STM32中我把地址写入0x02,。实际测试发现这个地址上的数据是对的,但是FPGA中0x02地址上的数据也变成了00。

块1存储区被划分为4个NOR/PSRAM区,这四个区在内部地址上是连续排列的。但是实际上每个区共用的是同一组地址线与数据线,因此需要有内外的一个地址映射,因此在STM32中实际上有两个地址,一个是在内部访问的地址,另外一个是实际地址线输出的地址。

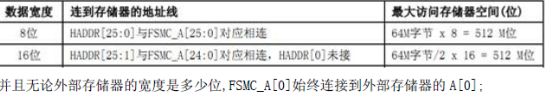

HADDR[27:0]对应的是需要转换到外部存储器的内部AHB地址线,其HADDR[27:26]位用于选择四个存储块之一。HADDR[25:0]包含外部存储器地址。HADDR是字节地址,而不同的外部存储器数据长度也不一样,因此在数据宽度为8位和16位时映射关系也不一样。

在数据宽度为8位时HADDR[25:0]与FSMC_A[25:0]对应相连,这时候在STM32中访问的地址和实际地址线产生的地址是一致的。而在16位数据宽度时HADDR[25:1]与FSMC_A[24:0]对应相连,HADDR[0]未接,这时候实际地址线上给出的地址为需要访问的偏移地址的一半。

经过测试,发现写数据时实际上是进行了多次写入,导致把后面的地址也给写上了,最终导致数据混乱,后来经过学长提醒,决定把访问的地址定义为16位的,原来是32位的,经过测试问题解决。

所以这儿也算是长了经验,因为我只用了8根地址线,为了避免可能的问题,地址最好定义成对应的位数。但是还是很纳闷为什么之前八位数据线读写的时候没有这个问题。

PART5结语

STM32作为新一代ARMCortex-M3核处理器,其卓越的性能和功耗控制能够适用于广泛的应用领域;而其特殊的可变静态存储技术FSMC具有高度的灵活性,对于存储容量要求较高的嵌入式系统设计,能够在不增加外部分立器件的情况下,扩展多种不同类型和容量的存储芯片,降低了系统设计的复杂性,提高了系统的可靠性。

我要赚赏金

我要赚赏金