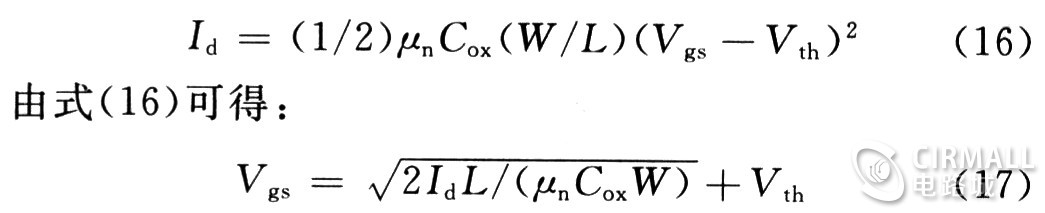

| 摘要:随着深亚微米CMOS工艺的发展,尺寸按比例不断缩小,对芯片面积的挑战越来越严重,双极型晶体管以及高精度电阻所占用的面积则成为一个非常严重的问题。鉴于此,本文提出了一款高精度的基准电压源的设计方案,经证实,该电路具备占用芯片面积小,精度高,可移植性强的优势特性。 0 引 言 随着集成电路的发展,一个高稳定、高精度的基准电压源变得越来越重要。特别是在D/A,A/D转换以及PLL电路中,温度稳定性和精度之间关系到整个电路的度和性能。 当今设计的基准电压源大多数采用BJT带隙基准电压源结构,以及利用MOS晶体管的亚阈特性产生基准电压源;然而,随着深亚微米CMOS工艺的发展,尺寸按比例不断缩小,对芯片面积的挑战越来越严重,双极型晶体管以及高精度电阻所占用的面积则成为一个非常严重的问题。在此,提出一种通过两个工作在饱和区的MOS管的栅源电压差原理,产生一个与温度成正比(PTAT)的电流,利用这个电流与一个工作在饱和区的二极管连接的NMOS晶体管的阈值电压进行补偿,实现了一个低温漂、高精度的基准电压源的设计。 1 NMOS晶体管的构成 两个工作在弱反型区的NMOS晶体管M1和M2的结构如图1所示。 其输出电压V0可以表示为:  式中:UT=kT/q;k为波尔兹曼常数;△V表示实际中晶体管失配引入的误差,是个常数,这里忽略它的影响。由此得到:  式中:  是由温度决定的倍增因子,后面将对其温度特性进行讨论。 是由温度决定的倍增因子,后面将对其温度特性进行讨论。对于NMOS晶体管M1和M2,其栅源电压分别为Vgs1和Vgs2,那么图3中电压为:  如果利用前面提到的两个工作在弱反型区的MOS管输出电压特性来控制两个工作在饱和区的NMOS的栅极电压Vgs1和Vgs2,使得:  式中:λ为比例常数。 将式(5)代入到式(3)可得:  对于参数KM1,它主要受晶体管迁移率λ的影响,通常被定义为:  式中:T为温度;α由工艺决定,典型值为1.5.将式(7)代人式(6)可得:  它为一个与温度无关的常数。 通过上面分析可知,此方法可以得到一个与温度成正比(PTAT)的电流I1.具体实现电路如图3所示。  图3电路中,M3~M6四个PMOS晶体管工作在饱和区,它们的宽长比相同。M1和M2两个NMOS晶体管工作在饱和区,它们的宽长比为(W/L)2/(W/L)1=m.通过调节电路,使得M7~M10四个NMOS晶体管工作在深线性区。现在讨论电路的工作原理。 对于X点和Y点的对地电压,可以分别表示为:  通过式(5)和式(15)可以看出,在这个电路中,式(5)的系数:  它是一个仅与器件尺寸有关,而与温度无关的常数。 通过式(9)和式(10)可知,此电路可以产生一个与温度成正比的电流。 2 基准电压的设计 对于一个工作在饱和区的二极管连接NMOS晶体管,如图4所示,它的Vgs=Vds流过它的饱和漏电流为:  对于MOS管的阈值电压Vth,它的一阶近似表达式可以表示为:  式中:Vth0为MOS管工作在零度时的阈值电压;aVT为一个与温度无关的常数;T-T0为温度变化量。对于一个MOS管的迁移率μn:它的大小可以表示为: μn=μn0(T/T0)-m (19) 式中:μn0为温度时MOS管的迁移率值;T0为零度;T为温度变化量;m为比例变化因子,它的典型值为1.5. 令式(10)中I1为式(17)中的Id,即:I1=Id,将式(10)、式(18)和式(19)代人式(17)整理可得:  从式(21)可看出,如果适当调节晶体管的宽长比W/L,使得зVgs/зT=0,即:  便可以得到一个高精度、与温度无关的Vgs,即Vref=Vgs=Vds.此思想设计的具体实现电路如图5所示。  对图5进行分析,NMOS晶体管M1和M2通过Vgs1和Vgs2产生漏电流Id1,再通过电流源M3和M7,使得它流入二极管连接的NMOS晶体管 M12,产生一个基准电压源Vref.在图5中,M3~M7五个晶体管尺寸相同,M1和M2晶体管的宽长比比例为1:m.式(21)中的W/L为图5中二极管连接M12管的宽长比。 |

共9条

1/1 1 跳转至页

[经验]一款高基准电压源的设计方案

关键词: 一款 高基准 电压源 设计 方案

共9条

1/1 1 跳转至页

回复

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 在FireBeetle2ESP32-C5上实现温湿度检测和显示被打赏¥20元 | |

| 在FireBeetle2ESP32-C5上实现光照强度检测及显示被打赏¥21元 | |

| 以FireBeetle2ESP32-C5实现数据识读播报被打赏¥19元 | |

| 【STM32F103ZET6】14:实测STM32F1的串口输出任务的挂起与恢复功能被打赏¥27元 | |

| Chaos-nano在压力容器监控系统中的项目应用被打赏¥23元 | |

| 基于FireBeetle2ESP32-C5的WS2812B彩色灯带控制被打赏¥21元 | |

| SWM221CBT7显示开发板驱动TFT显示屏被打赏¥19元 | |

| SWM221CBT7显示开发板驱动OLED屏显示被打赏¥19元 | |

| SWM221CBT7显示开发板及其使用被打赏¥20元 | |

| 揭秘Chaos-nano:ArduinoProMini轻量级操作系统开发框架深度解析与实战应用被打赏¥19元 | |