先进封装的出现,让业界看到了通过封装技术推动芯片高密度集成、性能提升、体积微型化和成本下降的巨大潜力。随着集成电路制造工艺沿着摩尔定律发展的步伐放缓,先进封装技术正成为集成电路产业发展的新引擎。

1. 集成电路与封装的发展

芯片由集成电路裸片(Die)与外围封装结构组成,二者共同决定了芯片的性能。国际半导体技术路线图(ITRS)指出,集成电路技术会沿More Moore(延续摩尔定律)和More than Moore(拓展摩尔定律)两个方向发展。延续摩尔定律的技术路线主要关注减小晶体管尺寸、增加集成电路密度;而拓展摩尔定律技术路线则更关注利用封装技术提高芯片和系统的集成度。

随着先进制程逐渐向原子尺寸逼近,短沟道效应和量子隧穿效应使晶体管的制造难度呈指数级增加。并且,随着制程提高,整体成本会大幅增加,5nm芯片设计成本已经是28nm芯片的8倍,这对于多数企业是难以承受的。纵观全世界,仅有台积电、三星和英特尔具备7nm制程工艺且有实力向3nm、2nm发展。因此,通过封装技术降低成本,将系统微型化、多功能化成为芯片产业发展的新引擎动力。

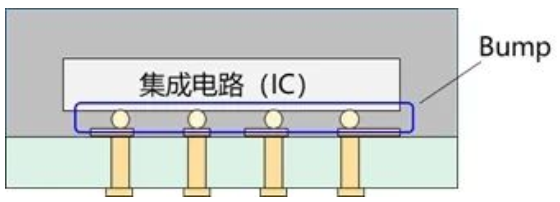

图1 芯片结构示意图

2. 半导体封装技术

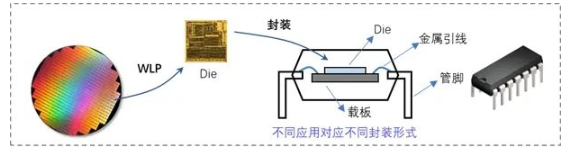

封装是将集成电路芯片包封在某一标准组件中的方法、结构和工艺,具有保护、固定、密封以及增强芯片电热性能的作用,是连接芯片与系统的桥梁,封装后的芯片可作为标准组件安装在印刷电路板(PCB)上实现应用。

图2 芯片封装示意图

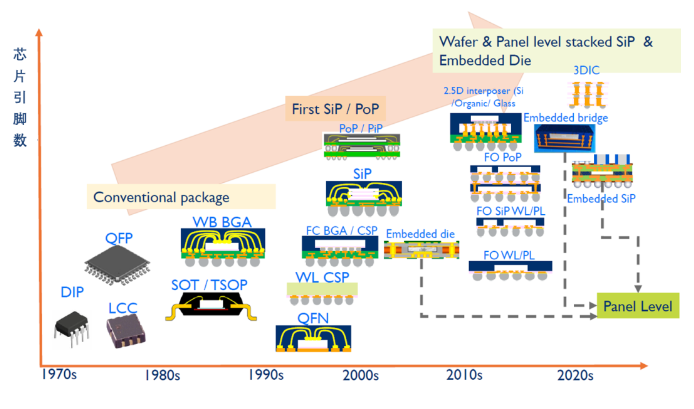

随着半导体工艺的发展,芯片引脚数逐渐增加,封装形式也由传统封装(引线框架作为载体,采用引线键合互连)向先进封装发展。在单芯片封装方面,先进封装较传统封装提升了芯片的集成密度和电气互联速度,降低了设计门槛,优化了功能搭配的灵活性。随着封装形式的多样化、组合化发展,先进封装不仅指单芯片封装,还包括将至少两颗以上芯片集成在一起的系统级封装(SiP)。

图3 芯片封装技术的发展(来源:yole)

表1 传统封装与先进封装

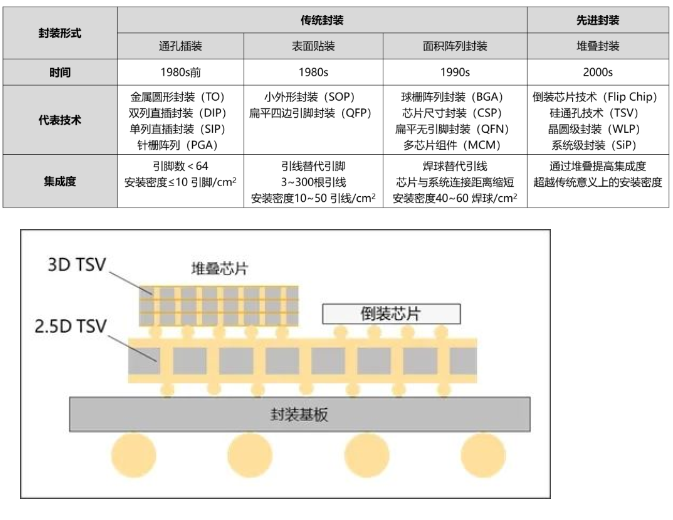

图4 单芯片封装与系统极封装(SiP)

3. 先进封装技术解析

目前,先进封装包含的代表技术包括倒装芯片技术(Flip Chip)、硅通孔技术(TSV)、晶圆级封装(WLP)、系统级封装(SiP)技术。

倒装芯片技术(Flip Chip)

Flip Chip是将芯片通过bump(凸点结构)直接与封装基板上的接口进行连接。

图5 Flip Chip示意图

相比传统引线键合封装,倒装主要有如下优势:1)性能方面,可减少引线带来的寄生电容,有利于提高频率、改善电学及热学性能;2)经济性方面,工艺简单,成本较低;3)空间方面,减小封装体积,使封装成品与芯片尺寸相当,实现芯片尺寸封装(Chip-Size Packaging,CSP)。

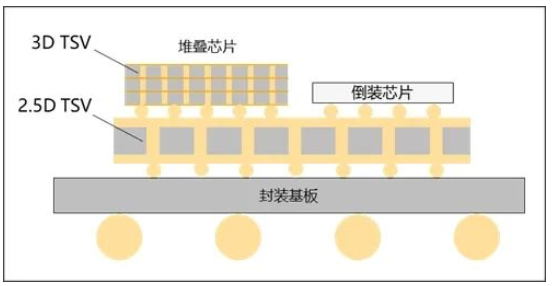

硅通孔技术(TSV)

TSV(Through Silicon Via, 硅通孔)技术主要用于立体封装,在垂直方向为芯片提供电气延伸和互连。按照集成类型的不同TSV分为2.5D和3D,2.5D通孔位于中介层,而3D通孔贯穿芯片本身,直接连接上下层芯片。

3D TSV技术使上下两片结构相同的芯片直接连接,从而实现大带宽、低时延的数据传输。这一特性与存储芯片的需求极度匹配,可提高存储芯片间的传输速度并降低功耗,已被大量应用于高端Flash和DRAM堆叠中。

2.5D TSV技术可以为同一封装体内的多个芯片提供大带宽、低时延的数据传输,与3D TSV结合的封装方式,已被大量应用于CPU、GPC当中。

图6 TSV技术示意图

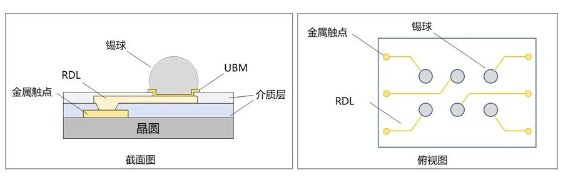

晶圆级封装(WLP)

传统封装工艺是先将晶圆切割为裸片再进行封装,而晶圆级封装是先进行封装再切割。晶圆级封装能明显缩小芯片封装后的尺寸,还能提升数据传输的速度与稳定性,被广泛应用于消费电子芯片。

RDL(ReDistribution Layer)重布线层作为晶圆级封装中的核心技术,起着XY平面电气延伸和互联的作用。在芯片设计和制造时,IO端口一般分布在芯片的边沿或者四周,为了便于与外界相连,需要在晶圆表面沉积金属层和相应的介质层,并形成金属布线,将IO端口重新排布到位置较宽松的区域,并形成面阵列排布。

图7 RDL技术示意图

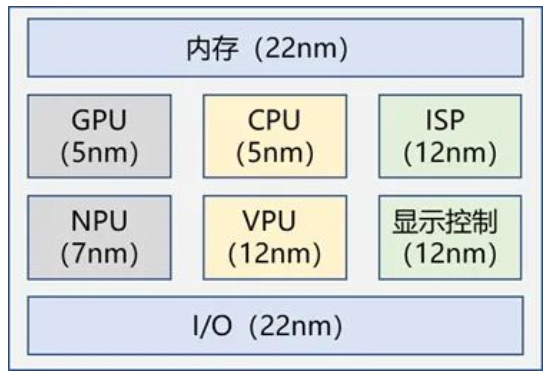

系统级封装(SiP)

SiP(System in Package,系统级封装)将多个具有不同功能的有源电子元件(通常是裸芯片)、无源器件及其他器件(MEMS或光学器件等)构成一个系统或子系统,并将多个系统组装到一个封装体内部,使其成为具有一定功能的单体封装件。从连接方式上看,倒装(FC)、重布线(RDL)和嵌入式(Embedded Die)是实现SiP的三条常见技术路线。

Chiplet技术是如今被广泛研究的SiP技术,它将单颗芯片的各功能区分解成多颗独立的芯片,并通过封装技术重新组成一个完整的系统。与传统的单一芯片相比,采用Chiplet技术的单颗芯片面积较小,可提高制造良率和实现异构集成。

图8 Chiplet技术示意图

4. 先进封装的应用案例

半导体行业已经基本实现分工精细化,产业链主要由设计、生产、封测等环节组成。先进封装推动前后道工艺相互渗透融合,具有较高技术壁垒和技术积累的厂商会向上下游工序延伸。如今,前、后道的头部厂商凭借各自优势入局,成为先进封装行业的主力军,其中,前道主要有英特尔、三星、台积电,后道主要有日月光、安靠、长电科技等。

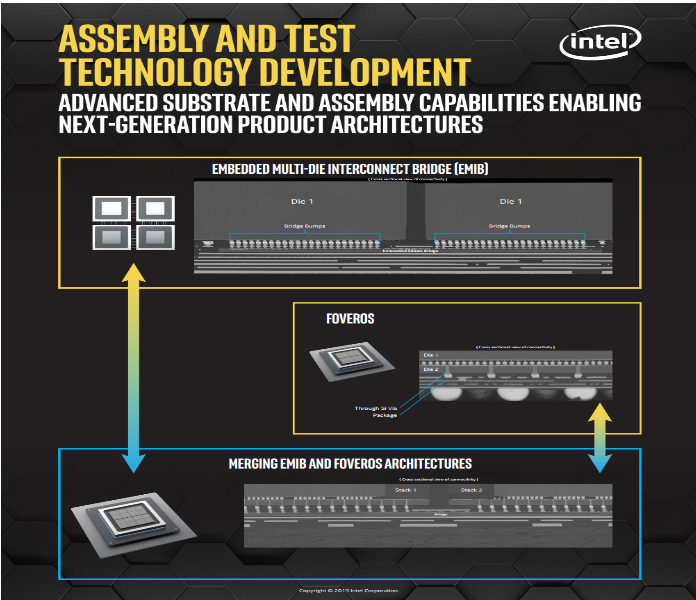

以英特尔为例,作为IDM代表性企业,在先进封装领域也不断推陈出新,而先进封装也是英特尔IDM2.0计划的关键点之一[7](图11)。2017年,英特尔推出的EMIB(Embedded Multi-die Interconnect Bridge 嵌入式多核心互联桥接)是其推进先进封装的重要一步。EMIB封装技术可以根据需要将CPU、IO、GPU甚至FPGA、AI等芯片封装到一起,能够把10nm、14nm、22nm等多种不同工艺的芯片封装在一起做成单一芯片,适应灵活的业务的需求。2019年,英特尔推出Foveros技术,开始将芯片竖直堆叠,进行横向和纵向之间的互连,一定意义上实现了3D堆叠。紧接着,在2019年的SEMICON West上,英特尔又将EMIB与Foveros技术结合。

图9 英特尔先进封装技术 (来源:英特尔官网)

总结

当前半导体领域处于高速发展的新阶段,先进封装是后摩尔时代系统集成与功能融合的关键路径,成为芯片制造与封装企业的新赛道,国内企业需抓住机会,在不断追赶国际半导体制造先进制程的同时,大力发展先进封装技术,在芯片制造领域缩短与世界领先水平的距离。

我要赚赏金

我要赚赏金