接这位楼主的提问,看了许多大虾们的解答,想提问一下,考虑到a的高电平会持续一段时间。如果要求非要在a的上升沿将count清零,如何实现呢?谢谢各位的支持!!!

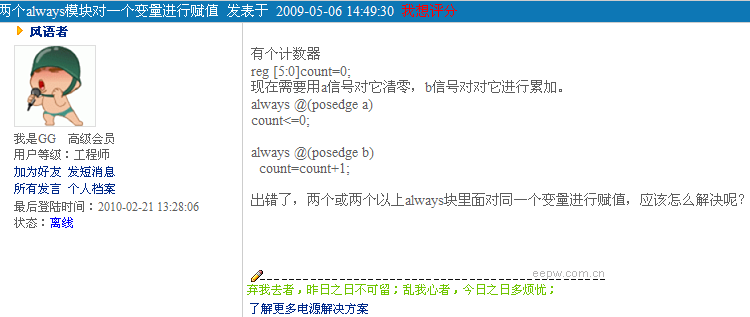

两个always模块的变量赋值问题

引入一个锁存器Lock,用来区分a的上升沿和高电平。

always @(posedge a or posedge b)

begin

if ( a==1 && Lock==0 )

begin

count <= 0;

Lock <= 1;

end

else

begin

count <= count + 1;

if ( a==0 )

Lock <= 0;

end

end

一般对于寄存器,复位是需要的,所以我这里省略了。

或者可以拆成两个写。这里采用同步复位

always @(posedge a or posedge b)

begin

if(rst==0)

begin

count <= 0;

end

else

begin

if ( a==1 && Lock==0 )

begin

count <= 0;

end

else

begin

count <= count + 1;

end

end

end

always @(posedge a or posedge b)

begin

if(rst==0)

begin

count <= 0;

end

else

begin

if ( a==1 && Lock==0 )

begin

Lock <= 1;

end

else

begin

if ( a==0 )

Lock <= 0;

end

end

end

好的。下面是我的程序,红色部分是增加的东西,增加了后就通过不了综合了。综合的问题是在第二个always上面涂红,问题是the logic for gpshighclkcnt [15:0] does not match a standard flip-flop.

module fuzhugen(gps,

gpshighclk,

rst,

fuzhu,

fuzhu1);

input gps;

input gpshighclk;

input rst;

output fuzhu; //增加一个fuzhu输出端口信号

output fuzhu1; //增加一个fuzhu1输出端口信号

reg fuzhu;

reg fuzhu1;

reg lockgpshigh;

reg [15:0] gpshighclkcnt;

always @ (posedge gps or posedge gpshighclk)

begin

if(rst)

begin

gpshighclkcnt<=16'd0;

fuzhu1<=(1==0);

fuzhu<=(0==1);

end

else

begin

if(gps && !lockgpshigh)

begin

gpshighclkcnt<=16'd0;

fuzhu<=(0==1);

fuzhu1<=(0==1);

end //gps信号上升沿时候,计数器清零,fuzhu和fuzhu1输出port清零

if(gps && gpshighclkcnt==16'd239)

begin

fuzhu <=(1==1);

end //当gps信号为高时并且计数器计数到239的时候fuzhu信号输出高电平

if(gps && gpshighclkcnt==16'd240)

begin

fuzhu1<=(1==1);

end //当gps信号为高时并且计数器计数到240的时候fuzhu1信号输出高电平

else

begin

gpshighclkcnt<=gpshighclkcnt+16'd1;

end

end

end

always @ (posedge gps or posedge gpshighclk)

begin

if(rst)

begin

gpshighclkcnt<=16'd0;

end

else

begin

if(gps && !lockgpshigh)

begin

lockgpshigh<=(1==1);

end

else

begin

if(!gps)

begin

lockgpshigh<=(1==0);

end

end

end

end

endmodule

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |