这是一份涉及芯片封装几乎所有关键概念的终极指南,它可以帮助您全面了解芯片的封装方式以及未来互连技术的发展趋势。

【内容目录】

1.电子封装简

2.早期封装类型

3.2D: 倒装芯片封装

4.2D:晶圆级封装

5.先进封装的兴起

6.2.1D/2.3D:超薄有机中介层

7.2.5D: 硅中介层、微凸点、硅通孔与硅桥

8.3D-IC封装

9.混合键合

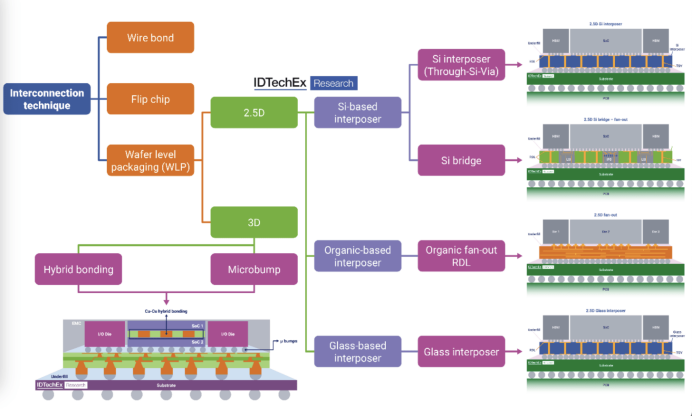

芯片封装类型(图片来源: IDTechEx Research)

电子封装(Electronic Packaging)简介

芯片是在硅片上制造的,但如果不能与外部世界建立接口,其本身是无法发挥任何作用的。芯片与外部的互连包括信号、接地和电源,这些连接通常通过芯片上的焊盘(pad)实现。根据所需的电气性能和外形尺寸,互连的实现方式可能有多种。

电子封装是指,将半导体器件封装起来,以保护其上的精密电路免受外部环境影响,并在电路与其他半导体器件或外部系统之间建立恰当的电气与机械接口,实现供电、信号连接或散热。

除了上述外在功能外,封装还有一个内在作用,即实现了从芯片凸点(bump)层级(10~100 微米量级)到电路板层级(毫米至厘米量级)的尺度过渡,因而封装也可称为一种尺度变换器。

根据所采用的封装类型不同,封装过程可能由半导体晶圆厂自行完成(即集成器件制造商IDM,Integrated Device Manufacturer),也可能外包给封测厂(OSAT,Outsourced Semiconductor Assembly and Test),由其负责封装制造、芯片装配及功能测试。目前,全球多数 OSAT 厂商集中在东南亚地区,知名企业包括 ASE(日月光)、Amkor(安靠) 和 JCET(长电科技,含原 StatsChipPAC)等。

理想情况下,封装不应对芯片的电气特性产生任何影响,然而现实并非如此。封装引脚及芯片与封装之间的内部互连都会影响芯片的电气性能。而且,随着晶体管的不断微缩,芯片间数据交换的数量与速率急剧增长,封装已成为系统性能的主要瓶颈之一。因此,尽量减少封装带来的电气损耗比以往任何时候都要关键。

晶体管的数量大致仍遵循摩尔定律,每两年翻倍一次,但封装互连的密度却远远落后。当封装技术的互连密度不足以支撑芯片上越来越密集的晶体管时,就会出现所谓的焊盘限制(pad-limited)设计困境。为解决连接问题,芯片制造商通常会被迫扩大芯片尺寸,而为了不浪费硅片,又在芯片上塞入更多的功能,例如额外的 SRAM。这样虽能带来一定系统层面的好处,但从长远来看,由于先进工艺节点下硅片成本不断攀升,这种做法不可持续。随着小芯片(chiplet,也称为芯粒)技术的兴起,电气封装技术的复杂度和重要性都变得尤为突出。

芯片核心区域以及焊盘限制问题

在下一部分,我们将回顾封装技术的起源,并逐步了解其复杂性如何演进到当今的地步。

早期封装类型

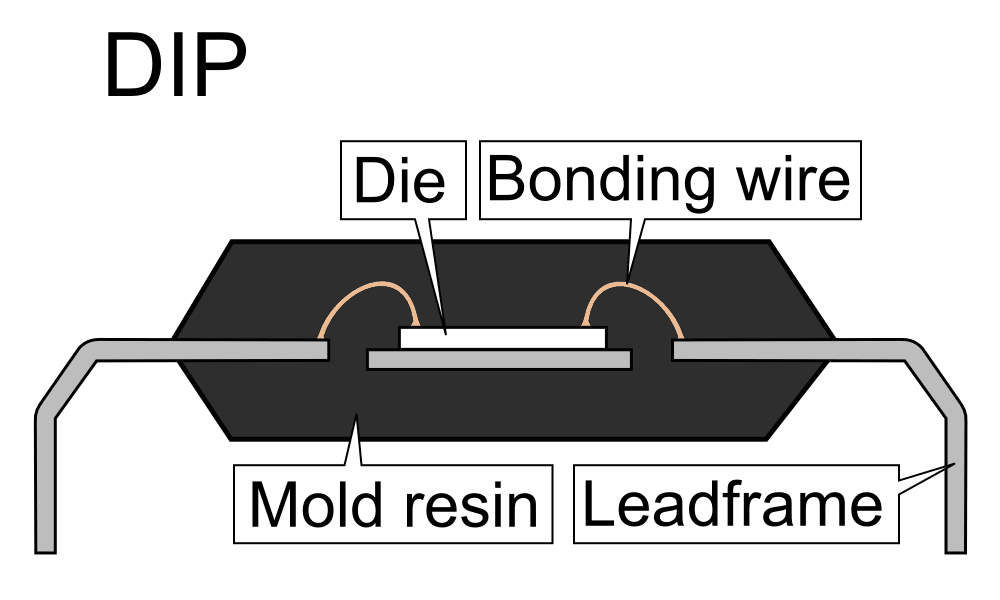

在70至80年代,最早的封装形式是双列直插式封装(DIP, Dual-Inline Package)。这种封装结构本质上由一个 L 形引线框架(leadframe) 和一个 中央芯片承载板(paddle) 组成,硅芯片被固定在该承载板上。从引线框架到芯片的连接通过极细的金属丝(称为金属键合线,bondwire)实现。整个封装随后被树脂覆盖,以提供机械保护。最终,引线框架被焊接到带有通孔(through-hole)的印刷电路板(PCB)上。

双列直插式封装(DIP)

英特尔4004 CPU(1971 年发布)是首个实现大规模集成的处理器,包含约 2,300 个晶体管,就采用了这种 DIP 封装。

Intel 4004 CPU采用DIP封装

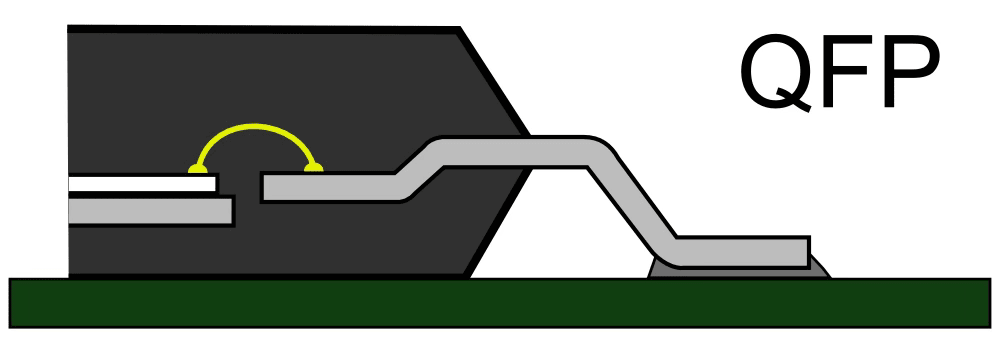

然而,DIP 封装的突出引脚和电路板上必须钻孔的设计即笨重又非常不便,于是这种结构逐渐被四边扁平封装(QFP, Quad-Flat Package)取代。QFP 采用类似“海鸥翼”(gull-wing)形状的引脚结构,整体更为扁平,并且无需在电路板上开孔。这种封装在80年代末至90年代初非常流行。例如著名的 Zilog Z80 CPU,它既有 DIP 封装版本,也有 44 引脚 QFP 版本。

QFP封装

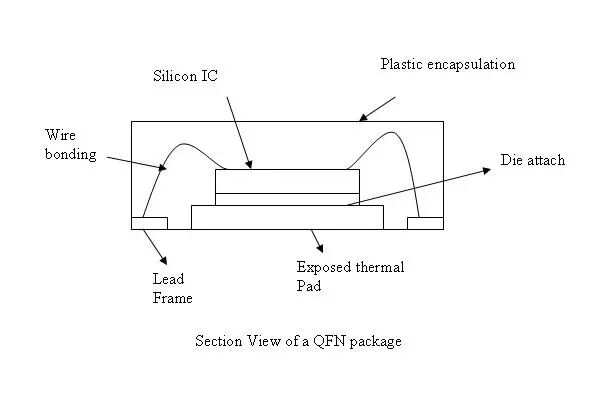

接下来的重要演进就是无引脚四边扁平封装(QFN, Quad-Flat No-Lead)。这种封装彻底取消了传统的长引脚结构,带来了三大优势:降低寄生电感;减轻重量与厚度;封装尺寸几乎与芯片本体相同。

在 QFN 封装中,引线框架是一整块金属板:一面与电路板相连,另一面通过金属键合线与芯片相连。由于寄生电感显著降低,这种封装能够应用于高频(低 GHz 范围)射频产品设计中。

QFN封装

QFN封装的另一大优点是优异的散热性能。承载芯片的金属板具有极高的热导率,其大面积接触面也可有效传导芯片热量。至今,QFN 封装仍被广泛用于电源、工业与汽车电子领域,因为相比尺寸、复杂性或高频,这些应用对散热性能的要求更关键。

除此之外,早期还有很多其他封装类型,如下面所列及其各种衍生变体:

· 薄型小外形封装(TSOP, Thin Small Outline Package)

· 无引脚芯片载体(LCC, Leadless Chip Carrier)

封装种类繁多,此处不一一介绍。虽然其中一些封装至今仍在使用,但真正带来封装技术质的飞跃的,是随后的倒装芯片(Flip-Chip)技术。

2D:倒装芯片封装(Flip-Chip Package)

90年代,一种被认为是芯片封装演进史上阶跃式革新的新技术逐渐成为主流,这就是倒装芯片技术。这种技术也被称为 C4(Controlled Collapse Chip Connection)。其核心思想是取消传统的金属键合线,改用焊锡球(solder balls)直接实现芯片与封装的电连接。这标志着芯片封装进入了一个全新的阶段:过去的键合线封装只能利用芯片四周的边缘进行连接,而倒装芯片技术则利用整个芯片表面进行互连,大幅提升了单颗芯片可用的连接数量。在传统键合结构中,芯片金属层及器件朝上(face-up);而在 C4 技术中,芯片被翻转,金属层和器件朝下(face down),直接面对封装基板。

技术原理

在倒装芯片封装中,焊锡球被布置在芯片的焊盘上。布置过程在整片硅晶圆(直径可达 12 英寸)上一次性完成,称为凸点工艺(bumping)。焊球之间的中心间距约为130~200 微米,称为凸点间距(bump pitch);而单位面积的焊球数量(每平方毫米的凸点数)被称为凸点密度(bump density),这是业界常用的另一项指标。

随后,整片晶圆被切割(dicing)成单个芯片,每个芯片上都带有焊球,准备与封装基板进行连接。

带焊球的切割好的芯片(图片来源: Intech Technologies)

现代封装基板的核心部分通常采用有机材料,最常用的是阻燃型的FR-4(Flame Retardant 4),这是一种具有自熄性的玻璃纤维编织材料。部分应用也采用无芯结构(Coreless Stackup)。

在基板核心材料的上下两面,会逐层叠加薄型聚合物绝缘膜。在这些薄膜之间沉积金属导线,并通过蚀刻形成贯穿不同金属层的微孔(via,本质上是连接不同层级金属的小型互连结构),从而在基板上构成多层金属结构,用于封装内部的金属连接布线。

目前最常用的绝缘膜材料是 Ajinomoto Build-up Film(ABF),由著名的味之素集团(Ajinomoto Group)生产。没错,就是那个以制造味精(MSG)闻名的公司。

倒装芯片基板所用的味之素积层膜ABF (图片来源:Ajinomoto Group)

与晶圆厂在硅片上常用的双镶嵌(dual damascene)金属互连工艺不同,封装基板的制造采用半加成工艺(SAP, Semi-Additive Process):先在已有金属结构上层压绝缘膜,再用激光在膜层上开出层间互连的通孔,最后通过电镀形成新一层金属线路。

装配流程

将带有焊球的晶粒(die,也称裸片)翻转,使其正面朝下贴合至封装基板。通过精确对位,确保芯片与基板实现可靠连接。

在传统贴装工艺中,通过加热使焊球回流(reflow):高温使焊锡瞬间熔化,借助液态锡的表面张力,芯片可自动微调位置并与封装基板形成稳固连接,随后焊锡冷却固化。然而,随着芯片面积增大或焊点间距缩小,热压键合(Thermal Compression Bonding, TCB)技术正逐渐成为更主流的贴装方案。

键合完成后,在芯片与基板间的缝隙中注入毛细底部填充胶(Capillary Underfill, CUF)。由于芯片与基板的热膨胀系数(CTE)存在差异,工作温度变化时两者胀缩程度不同,会在焊点处产生机械应力。CUF材料能够提供必要的机械支撑与缓冲保护,防止焊点开裂或芯片从基板上剥离。

后续工序还包括安装热扩散片(heat spreader,若设计需要)、贴装焊球阵列(Ball Grid Array, BGA)等步骤。最终完成的封装器件即可进入电路板组装流程。

倒装芯片封装工艺流程示意图(图片来源:Anysilicon.com)

倒装芯片技术的主要优势包括:

· 低寄生效应:相比传统引线框架或 QFN 封装中数百微米长的键合线,焊锡球高度仅约 50~70 微米。这极大地降低了互连电阻和电感,使封装适用于高性能电路。

· 紧凑的尺寸:由于取消了键合线,芯片尺寸几乎可与封装尺寸相等。整体封装更加小巧、轻便,无需像 DIP 或 QFP 那样使用长引线金属。

·多芯片集成:借助 ABF 技术在封装基板上实现金属互连,可在同一基板上放置多个晶粒,并通过金属走线互联。这使具有不同功能的芯片能在二维平面上集成于单一封装中。

英特尔的Tiger Lake移动处理器由多个芯片封装而成。较大的芯片是CPU,较小的芯片是平台控制器中心(PCH),即chipset(来源:英特尔)

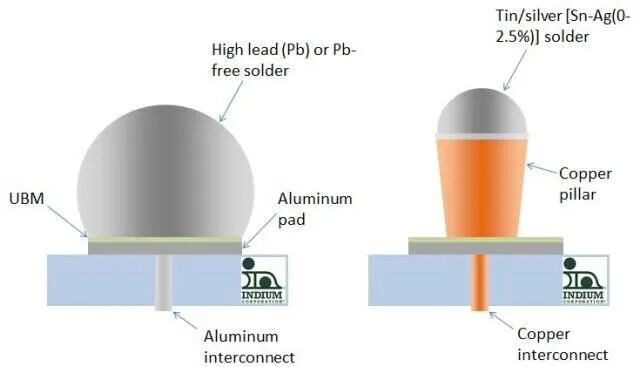

利用铜柱(Copper Pillar)减小凸点间距

随着硅芯片上器件尺寸的不断缩小,晶体管数量不断增加,从芯片引出的信号数量也随之攀升。要在芯片单位面积内布置更多互连凸点,就必须减小凸点尺寸与间距。

然而,传统焊锡球的球形结构在缩小间距时存在限制。为了解决这一问题,工程师引入了铜柱(Copper Pillar)+ 焊锡帽(Solder cap)的结构来替代纯焊锡球。

这种改进带来了显著效果,采用铜柱结构后,凸点间距可以缩小到 100 微米以下;铜柱的圆柱形几何结构使得凸点能够更加紧密地排列;缩小铜柱直径可以进一步提升凸点密度。

铜柱取代焊锡球后的封装结构示意图(图片来源:Indium Corporation)

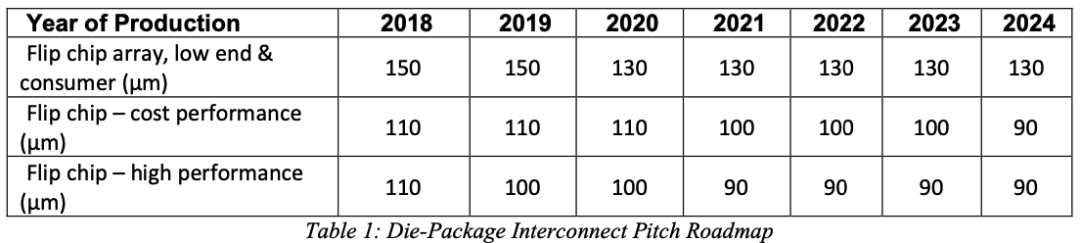

根据《2024 异构集成路线图》的预测,在标准核心封装中,倒装芯片凸点间距预计不会显著低于 90 微米。原因在于,这一下限受到封装基板制造工艺线宽/间距能力的限制。在标准封装基板上,要实现更小的特征尺寸难度极高。当凸点间距进一步缩小时,就必须采用更精细的互连技术,例如微凸点(Micro-Bump),以及支持超精细互连的基板结构(如中介层,Interposers)。这些技术将在后续章节中进一步探讨。

2D:晶圆级封装

晶圆级封装是一种在芯片仍处于晶圆状态时,直接在晶圆上构建封装结构的技术演进形式。也就是说,不像倒装芯片封装(Flip-Chip)先制造独立的封装再将芯片装入,晶圆级封装是在晶圆上原地完成封装流程。

基本原理与工艺流程

与倒装芯片封装类似,芯片首先通过硅工艺制造完成,并从晶圆上切割下来。那些通过测试的良品晶粒(Known-Good Die)会正面朝上(非翻转)放置在一片空白晶圆上,这片基底晶圆通常称为重组晶圆(Reconstituted Wafer)。

然后,整个重组晶圆会被覆盖上一层介电模塑层(dielectric mold layer)。多余的模塑材料会被研磨掉(grinding back),以露出芯片表面的铜凸点;或者,在需要与芯片焊盘连接的区域,通过开通孔的方式在模塑层中形成通路。

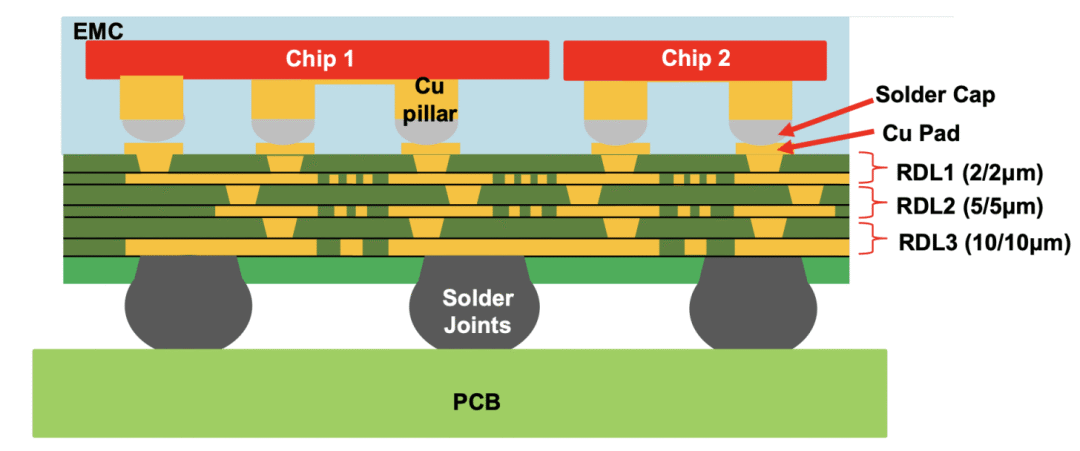

接下来,在该介电层上沉积金属走线层,形成一个新的互连层,称为重布线层(Redistribution Layer, RDL)。 在形成 RDL 后,晶圆会进入凸点工艺步骤。

带重分布层(RDL)的扇出型晶圆级封装(图片来源:ASE)

通过在芯片表面构建 RDL 层,封装设计不再受限于倒装芯片技术中的凸点间距。

在重组晶圆上,芯片之间的间距可以被适当放大,从而制造出比芯片本体更大的封装结构。换句话说,RDL 将芯片重分布到更大面积上,从而为放置更多的焊锡球或铜柱提供了空间。

RDL 的互连线宽与间距虽不如芯片内金属化结构那样精细,但一般工艺可达10/10 微米;高端 RDL 技术甚至可实现2/2 微米。此外,还可以构建多层 RDL 金属层,实现更复杂的信号走线。该技术并不限于单一芯片类型,不同制程节点、不同功能的芯片都可以通过 RDL 互连集成在同一封装中。

最后,带 RDL 层的芯片会从重组晶圆上再次切割,并翻转贴装到 PCB 基板上,如下图所示。

用于异构集成的面板级扇出 RDL-First封装

这种封装将芯片连接向外扇出(fan-out)到更大面积,从而简化了整体封装设计,通常称之为扇出型晶圆级封装(FOWLP, Fan-Out Wafer-Level Packaging),或晶圆级芯片封装(WLCSP, Wafer-Level Chip Scale Packaging)。

在某些应用场景中,若所需的信号、电源/接地焊球数量较少,且能容纳在晶粒面积内,则可采用晶圆级扇入型封装(Fan-In WLP)。这种方式可在芯片尺寸范围内(或略大)完成封装,从而节省空间与成本,常用于边缘计算与移动设备等应用。

晶圆级封装的几种主要工艺流程如下:

1.Chip-First(芯片优先):

这是前面所述的标准流程。先将芯片安装在重组晶圆上,再在其上构建 RDL 层。完成RDL 层后,再将整个“芯片+封装”从晶圆中切割出来。其优点是工艺成本较低,但缺点也不少,如在 RDL 加工过程中,芯片可能发生偏移或错位;较大的芯片可能因热应力而翘曲变形。因此,该工艺更适合用于较小的芯片与简单封装。由于在 RDL 制程前就已使用良品芯片,RDL 的良率必须很高,否则成本效益会显著降低。

Chip-Last(芯片后置)

此流程类似早期的倒装芯片工艺,先在重组晶圆上构建RDL层,再将切割后的芯片翻转贴装到 RDL 上并进行模塑。其优点在于,芯片不会经历多次 RDL 加工中的高温循环,可保持硅芯片的原始结构完整; RDL 层可在贴片前进行检测,避免因缺陷导致良率损失; 而且,可在 RDL 上形成更精细的特征(L/S 可达2/2 µm),从而提升电气性能。其劣势在于工艺步骤较多,整体成本较高。

Chip-Last 扇出型封装示意图(图片来源:ASE)

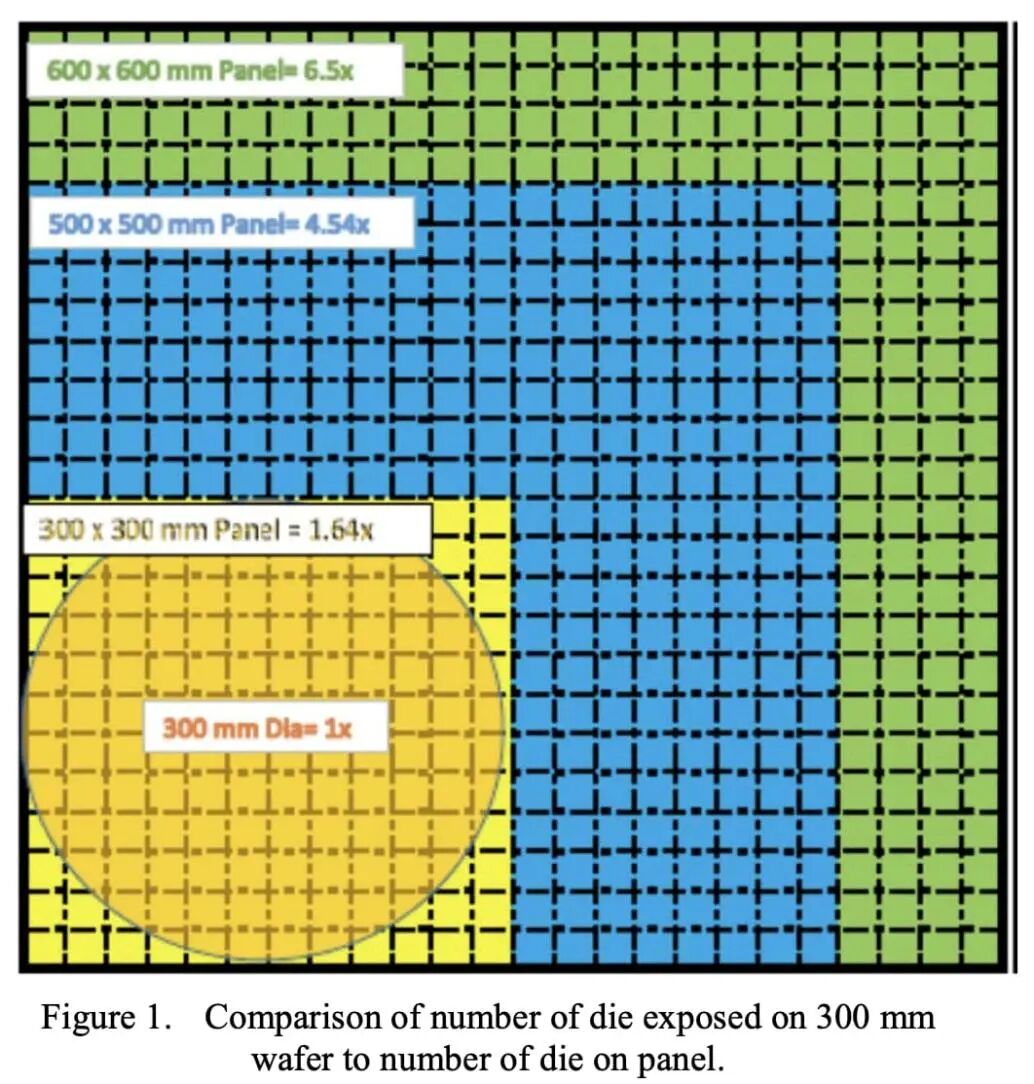

3.Panel-Level Fan-Out(面板级扇出封装,PLFO)

前两种方法都使用圆形晶圆(最大 300 mm 直径),面积利用率有限。PLFO 技术则采用矩形大面板(最大 600 mm × 600 mm)代替晶圆。由于面积利用率更高,每片面板的封装数量可提升约 6.5 倍,因此单个封装成本可降低约 20%。不过,这项新技术仍面临很多挑战,例如设备与生产线需升级以支持大尺寸矩形面板;目前可支持的 RDL 层数较少,线宽/间距仍较大。尽管如此,对于电源管理 IC(PMIC)等对高密度要求不高的应用,现有 PLFO 技术已足够提供一种低成本、高产量的晶圆级封装方案。

600×600 mm² 面板上的面板级封装,每次可制造多于晶圆 6.5 倍的封装(图片来源:StatsChipPAC)

此外,还有“正装(face-up)”与“倒装(face-down)”芯片放置等多种变体流程,本文暂不做深入讨论。

先进封装的兴起

毋庸置疑,传统封装在过去几十年中已经很好地满足了硅芯片不断变化的需求。但在最近的十年,封装变得愈发关键,其驱动因素包括:

· 功能拆分(Disaggregation):随着摩尔定律的发展放缓,以及先进制程下大尺寸晶粒成本的日益高昂,业界开始倾向于将单一大型芯片拆分成多个较小的芯片,即chiplet芯粒。

· 异构集成(Heterogeneous Integration):由于不同的 IP 模块并不总能随制程节点一起缩放,为了节省移植成本,理想的做法是让不同模块采用最适合它们的不同硅节点,这就催生了在同一封装上混搭不同芯粒的需求。

· 存储墙(Memory Wall)问题:内存带宽的需求远远超过了带宽扩展的速度。高性能处理器为了获得更高的内存带宽,必须将内存尽可能靠近计算单元集成,因此演变出在封装上整合高带宽内存(HBM)的方法,而这在传统封装技术中是无法实现的。

· 打破光罩极限(Reticle Limit):AI 和云计算等应用推动了单封装计算能力的极限。由于单颗晶粒的尺寸受到光罩面积的物理限制,因此需要通过在一个封装内集成更多芯片,并使它们协同工作如同一颗超大芯片的方式来突破这一瓶颈。

上述需求促成了一系列新技术的诞生,我们统称为先进封装(Advanced Packaging)。在本系列的下篇中,将介绍这一领域的主要技术分支。

我要赚赏金

我要赚赏金