module Display(clk,data,addr,read_en,write_en,data_out,seg,lbit);

input clk;

input read_en,write_en;

input [7:0]data;

input [3:0]addr;

output [7:0] seg;

output [7:0] lbit;

output [7:0]data_out;

reg [7:0]data_in[7:0];

reg [7:0]seg;

reg [7:0]lbit;

reg[7:0]data_out;

reg [7:0]state;

parameter S0 = 1, S1 = 2, S2 = 4,S3 = 8, S4 = 16,S5 = 32, S6 = 64, S7 = 128;

reg [31:0]clk_div;

initial

begin

data_in[0]=249;

data_in[1]=164;

data_in[2]=255;

data_in[3]=255;

data_in[4]=255;

data_in[5]=255;

data_in[6]=255;

data_in[7]=255;

state=S0;

clk_div=0;

end

always @ (state) begin

case (state)

S0:begin

lbit = 254;

seg = data_in[0];

end

S1:begin

lbit = 253;

seg = data_in[1];

end

S2:begin

lbit = 255-S2;

seg = data_in[2];

end

S3:begin

lbit = 255-S3;

seg = data_in[3];

end

S4:begin

lbit = 255-S4;

seg = data_in[4];

end

S5:begin

lbit = 255-S5;

seg = data_in[5];

end

S6:begin

lbit = 255-S6;

seg = data_in[6];

end

S7:begin

lbit = 255-S7;

seg = data_in[7];

end

endcase

end

always @ (posedge clk ) begin

if(clk_div>50_000)begin

clk_div=0;

case (state)

S0:

state <= S1;

S1:

state <= S2;

S2:

state <= S3;

S3:

state <= S4;

S4:

state <= S5;

S5:

state <= S6;

S6:

state <= S7;

S7:

state <= S0;

endcase

end

else

clk_div=clk_div+1;

if(write_en)begin

//write regs

case (addr)

0001:

data_in[0] <= data;

0010:

data_in[1] <= data;

0011:

data_in[2] <= data;

0100:

data_in[3] <= data;

0101:

data_in[4] <= data;

0110:

data_in[5] <= data;

0111:

data_in[6] <= data;

0100:

data_in[7] <= data;

default:

data_in[0] <= data_in[0];

endcase

end

if(read_en) begin

case (addr)

0001:

data_out <= data_in[0];

0010:

data_out <= data_in[1];

0011:

data_out <= data_in[2];

0100:

data_out <= data_in[3];

0101:

data_out <= data_in[4];

0110:

data_out <= data_in[5];

0111:

data_out <= data_in[6];

0100:

data_out <= data_in[7];

default:

data_out <= data_in[0];

endcase

end

end

endmodule

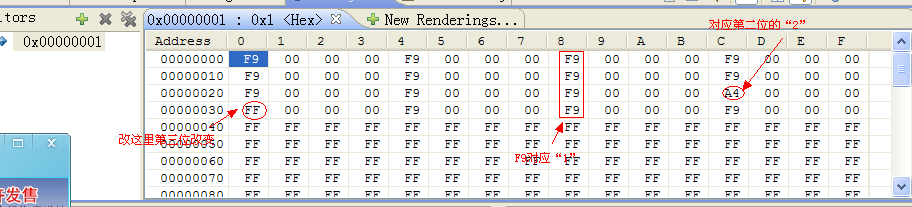

这是硬件的源代码。其中第一二位默认显示“1”和“2”

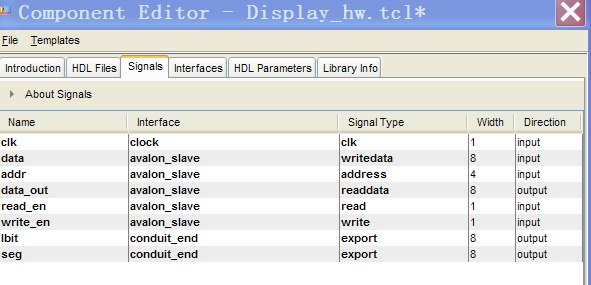

这是设置signals

这是设置signals静态地址对齐。

在软件利用这句话写的时候没有任何现象.IOWR(DISPLAY_0_BASE,0x30,5); //display(可以认为程序里就这一句话)

下面是debug时memory窗口

很奇怪,我在display.v里用了8个寄存器,它们的地址是怎么分配的呢?

为什么IOWR时memory没有任何改变?

恳请高手帮忙

我要赚赏金

我要赚赏金