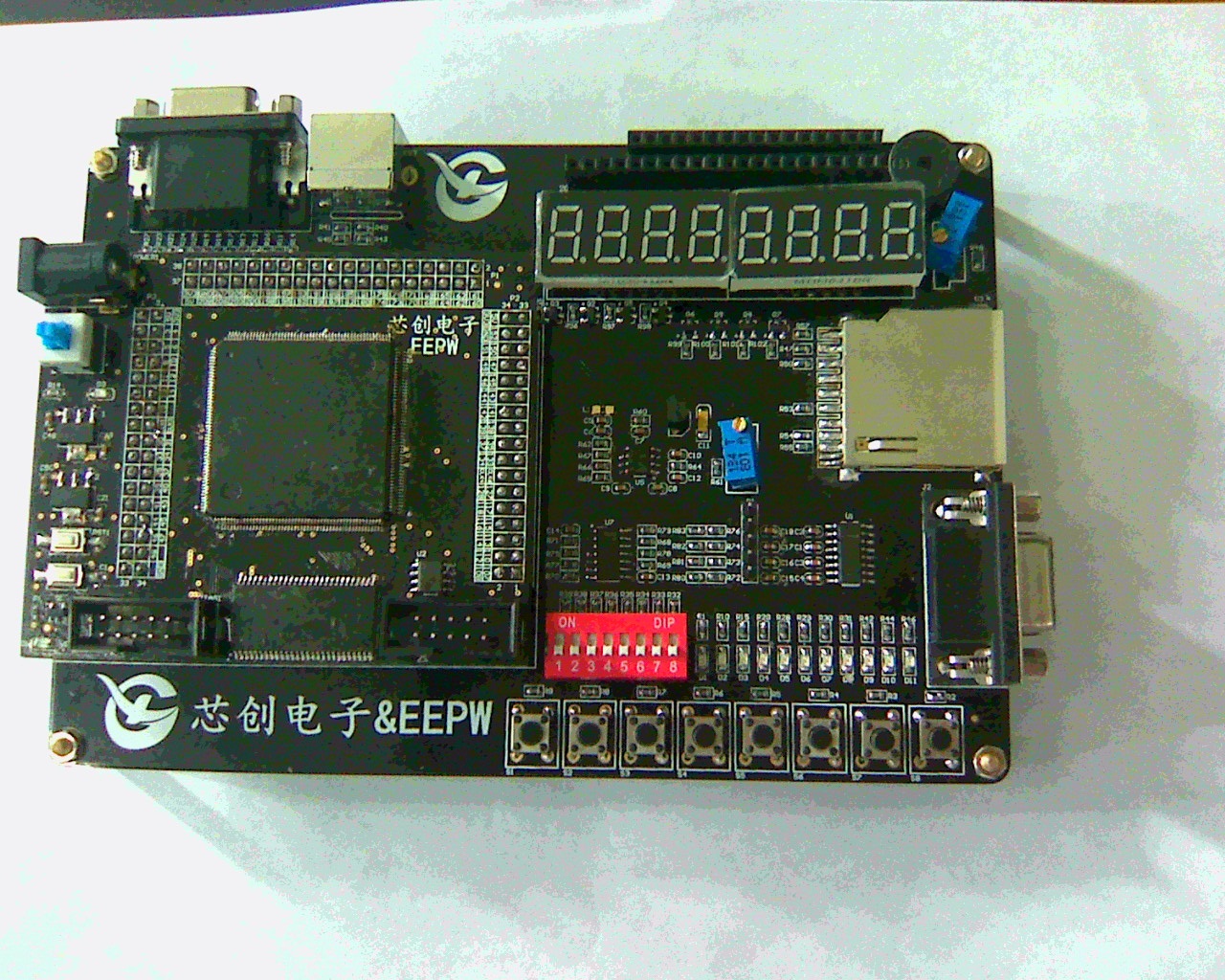

核心板与接口板PCB图片——————————————————————2楼

FPGA开发板焊接完成 ———————————————————————7楼

LED篇----花样彩灯--------------------------------------------------------------------8楼

按键篇-----------------------------------------------------------------------------------9楼

FPGA开发板焊接完成 ———————————————————————7楼

LED篇----花样彩灯--------------------------------------------------------------------8楼

按键篇-----------------------------------------------------------------------------------9楼

8个LED先闪烁几次,然后依次从左到右点亮,从右至左点亮,从左至右连续点亮,从右至左连续点亮。

需要说明的的是上传的sof,使用的是Y1的晶振。

//

module led_run(sys_clk,sys_rstn,led);

input sys_clk;

input sys_rstn;

output reg [7:0]led;

//计数器

reg [25:0]cnt;

always@(posedge sys_clk )

begin

if(cnt==26'd49999999)

cnt<=26'd0;

else

cnt<=cnt+1'd1;

end

//1Hz

reg clk_1s;

always@(posedge sys_clk )

begin

if(cnt<=26'd25000000)

clk_1s<=1'd0;

else

clk_1s<=1'd1;

end

parameter start=8'd0;

parameter right_set=8'd1;

parameter shift_right=8'd2;

parameter run_right=8'd3;

parameter left_set=8'd4;

parameter shift_left=8'd5;

parameter run_left=8'd6;

reg [25:0]delay_cnt;

reg [7:0] state;

always@(posedge clk_1s or negedge sys_rstn)

begin

if(!sys_rstn)

begin

delay_cnt<=25'd0;

led<=8'b0000_0000;

state<=8'd0;

end

else

begin

delay_cnt<=delay_cnt+1'd1;

case(state)

start:begin

led=~led;

if(delay_cnt==25'd5)

begin

state<=right_set;

delay_cnt<=25'd0;

end

else

state<=start;

end

right_set:begin

led<=8'b1111_1110;

state<=shift_right;

delay_cnt<=25'd0;

end

shift_right:begin

led<={led[6:0],led[7]};

if(delay_cnt==25'd6)

begin

state<=shift_left;

delay_cnt<=25'd0;

end

else

state<=shift_right;

end

shift_left:begin

led<={led[0],led[7:1]};

if(delay_cnt==25'd6)

begin

state<=run_right;

delay_cnt<=25'd0;

end

else

state<=shift_left;

end

run_right:begin

led<=led<<1;

if(delay_cnt==25'd6)

begin

state<=left_set;

delay_cnt<=25'd0;

end

else

state<=run_right;

end

left_set:begin

led<=8'b0111_1111;

state<=run_left;

delay_cnt<=25'd0;

end

run_left:begin

led<=led>>1;

if(delay_cnt==25'd6)

begin

state<=start;

delay_cnt<=25'd0;

end

else

state<=run_left;

end

endcase

end

end

endmodule

//功能说明

//按键消抖、有按键时8个LED灯翻转、按S1数码管显示数据减一,按S2数码管显示数据加一wire [1:0]key_an=key_rst_r&~key_rst;

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |