RainlyWy进程贴-(万年历LCD显示带按键设置保存)

1.开发板焊接(12.10.1---12.10.7) ---------- 2楼

2.LED流水(12.10.17) ---------- 3楼

3.LED闪烁,跑马,流水组合(12.10.18)-------- 6楼

4.按键消抖控制LED灯(12.10.18)---------------- 7楼

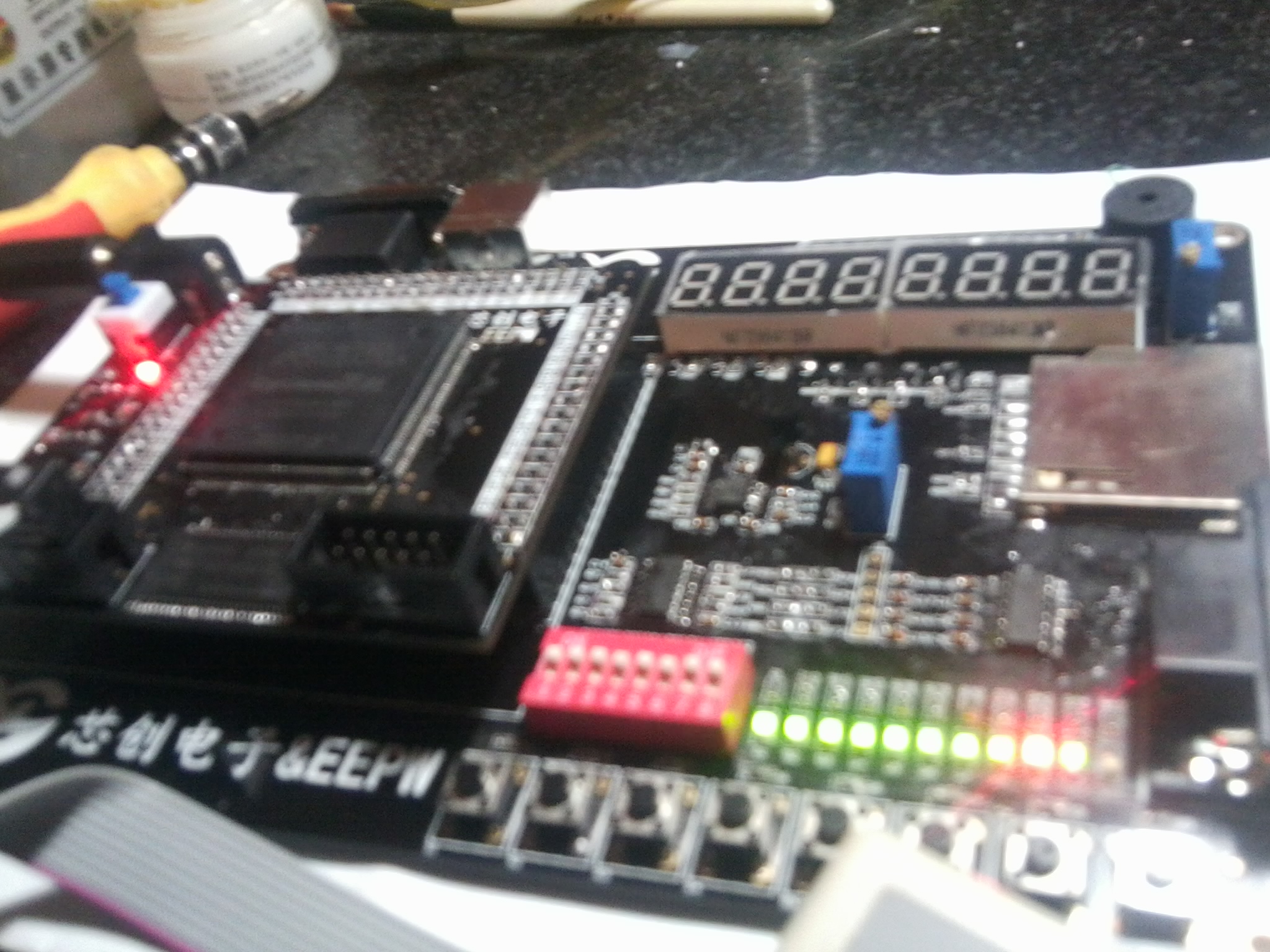

5.数码管静态显示(12.10.19)------------------- 9楼

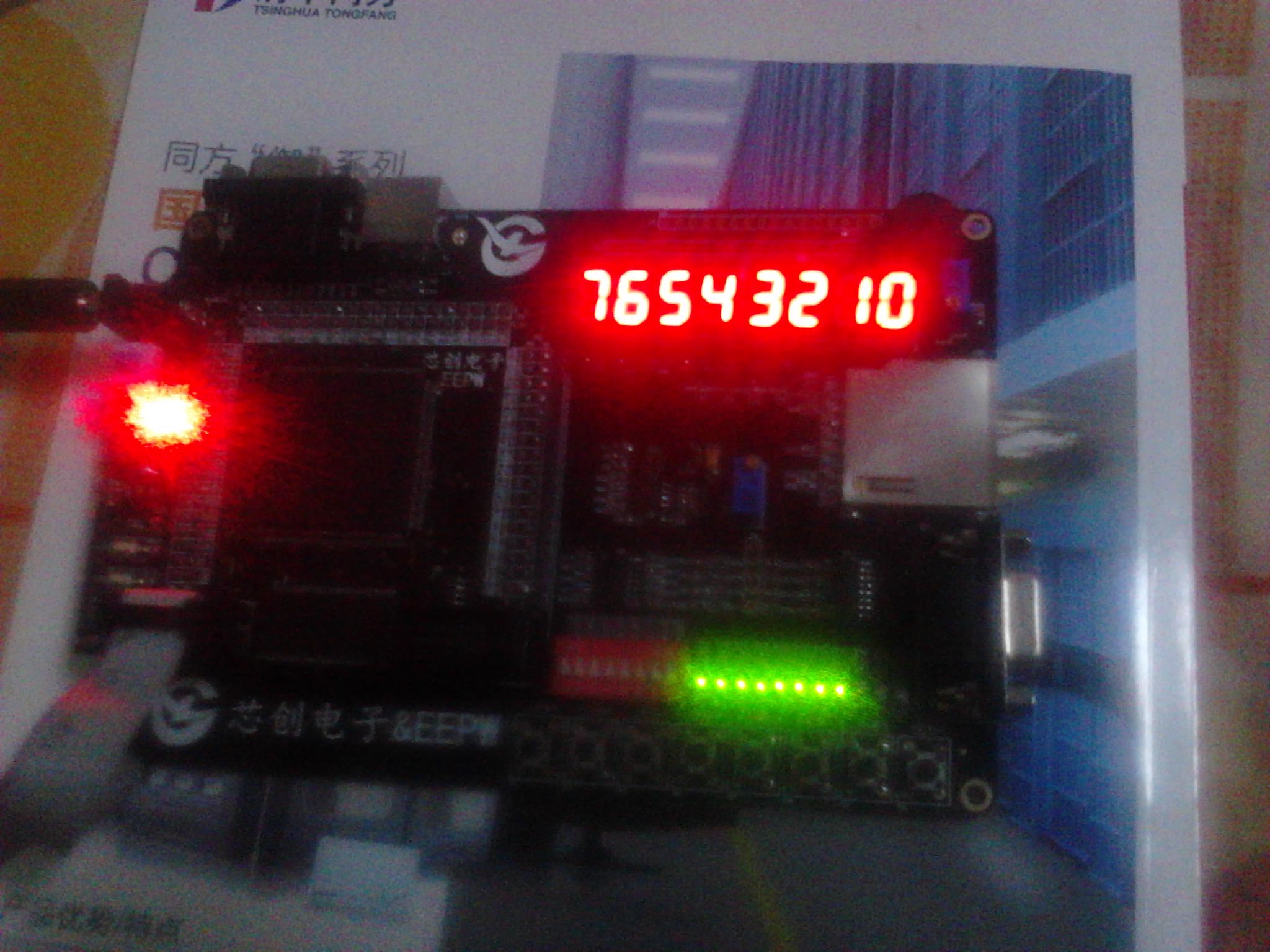

6.数码管动态显示-时钟显示(12.10.19)-------- 10楼

7.蜂鸣器-警报声(12.10.20)------------------ 11楼

8.蜂鸣器-电子琴(12.10.20)------------------ 13楼

9.蜂鸣器-自动播放音乐-祝你生日快乐(12-10-21) 16楼

10.LCD1602显示(12-10-23)------------------- 17楼

11.串口通信-协议控制LED流水------------------ 19楼

12.万年历-数码管-1602显示-带按键设置保存时间- 22楼

-----------隔断-------------------隔断-----------------------

12-11-20 好久没上来了 公司一直忙啊忙的,今天终于有空上来瞧瞧了,发现自己的帖子跑第三页了都,赶紧冒一下喽!!!!!

关键词: RainlyWy 进程 万年历 显示 按键 设置

源码:

module aaa(

input sysClk,

input sysReset,

output wire [7:0] led,

output wire power_led,

output wire work_led

);

parameter DELAY = 5000000;

reg [31:0] delay_cnt = 0;

always @(posedge sysClk,negedge sysReset)

begin

if(!sysReset)

delay_cnt <= 32'd0;

else if(delay_cnt >= DELAY)

delay_cnt <= 32'd0;

else

delay_cnt <= delay_cnt + 1'b1;

end

reg calWorkLed = 0;

reg calPowerLed = 0;

always @(posedge sysClk,negedge sysReset)

begin

if(!sysReset)

begin

calWorkLed <= 1'b0;

calPowerLed <= 1'b0;

end

else if(delay_cnt >= DELAY)

begin

calWorkLed <= ~calWorkLed;

end

end

reg [3:0] sta = 0;

reg [7:0] calLed = 8'b11111111;

reg [7:0] OverCnt = 0;

always @(posedge sysClk)

begin

if(!sysReset)

calLed <= 8'b11111111;

else if(delay_cnt >= DELAY)

begin

case(sta)

0:

begin

OverCnt <= OverCnt + 1;

calLed <= ~calLed;

if(OverCnt >= 6)

begin

calLed <= 8'b11111110;

OverCnt <= 8'd0;

sta <= 4'd1;

end

end

1:

begin

OverCnt <= OverCnt + 1;

calLed <= {calLed[6:0],calLed[7]};

if(OverCnt >= 7)

begin

calLed <= 8'b1111_1111;

OverCnt <= 8'd0;

sta <= 4'd2;

end

end

2:

begin

OverCnt <= OverCnt + 1;

calLed <= {1'b0,calLed[7:1]};

if(OverCnt >= 7)

begin

calLed <= 8'b0000_0000;

OverCnt <= 8'd0;

sta <= 4'd3;

end

end

3:

begin

OverCnt <= OverCnt + 1;

calLed <= {calLed[6:0],1'b1};

if(OverCnt >= 7)

begin

calLed <= 8'b0111_1111;

OverCnt <= 8'd0;

sta <= 4'd4;

end

end

4:

begin

OverCnt <= OverCnt + 1;

calLed <= {calLed[0],calLed[7:1]};

if(OverCnt >= 7)

begin

calLed <= 8'b1111_1111;

OverCnt <= 8'd0;

sta <= 4'd0;

end

end

endcase

end

end

assign led = calLed;

assign power_led = calPowerLed;

assign work_led = calWorkLed;

endmodule

源码:

1.顶层

module aaa(

input sysClk,

input sysReset,

input [7:0]key,

output wire [7:0] led,

output wire power_led,

output wire work_led

);

parameter DELAY = 5000000;

reg [31:0] delay_cnt = 0;

always @(posedge sysClk,negedge sysReset)

begin

if(!sysReset)

delay_cnt <= 32'd0;

else if(delay_cnt >= DELAY)

delay_cnt <= 32'd0;

else

delay_cnt <= delay_cnt + 1'b1;

end

reg calWorkLed = 0;

reg calPowerLed = 0;

always @(posedge sysClk,negedge sysReset)

begin

if(!sysReset)

begin

calWorkLed <= 1'b0;

calPowerLed <= 1'b0;

end

else if(delay_cnt >= DELAY)

begin

calWorkLed <= ~calWorkLed;

end

end

//assign led = key;

assign power_led = calPowerLed;

assign work_led = calWorkLed;

WipeJitter wipeJitter0(.clk(sysClk),.rstn(sysReset),.key(key[0]),.key_v(led[0]));

WipeJitter wipeJitter1(.clk(sysClk),.rstn(sysReset),.key(key[1]),.key_v(led[1]));

WipeJitter wipeJitter2(.clk(sysClk),.rstn(sysReset),.key(key[2]),.key_v(led[2]));

WipeJitter wipeJitter3(.clk(sysClk),.rstn(sysReset),.key(key[3]),.key_v(led[3]));

WipeJitter wipeJitter4(.clk(sysClk),.rstn(sysReset),.key(key[4]),.key_v(led[4]));

WipeJitter wipeJitter5(.clk(sysClk),.rstn(sysReset),.key(key[5]),.key_v(led[5]));

WipeJitter wipeJitter6(.clk(sysClk),.rstn(sysReset),.key(key[6]),.key_v(led[6]));

WipeJitter wipeJitter7(.clk(sysClk),.rstn(sysReset),.key(key[7]),.key_v(led[7]));

endmodule

2.消抖模块

module WipeJitter(

input clk,

input rstn,

input key,

output reg key_v

);

//delay key

reg key_d = 0;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

key_d <= 1'b0;

else

key_d <= key;

end

//generate nenedge key

reg negeKey = 0;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

negeKey <= 1'b0;

else

negeKey <= (key_d == 1'b1) & (key == 1'b0);

end

reg [19:0] DelayCnt = 0;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

DelayCnt <= 20'd0;

else if((negeKey == 1'b1) | (key == 1'b1))

DelayCnt <= 20'd0;

else if(DelayCnt == 500000)

DelayCnt <= DelayCnt;

else if(key == 1'b0)

DelayCnt <= DelayCnt + 1;

end

always @(posedge clk,negedge rstn)

begin

if(!rstn)

key_v <= 1'b1;

else if(DelayCnt == 500000)

key_v <= 1'b0;

else

key_v <= 1'b1;

end

endmodule

数码管静态显示:

源码:

module aaa(

input sysClk,

input sysReset,

output [7:0] led,

output [7:0] SEG,

output [7:0] DIG

);

parameter DELAY = 10000;

reg [31:0] delay_cnt = 0;

always @(posedge sysClk,negedge sysReset)

begin

if(!sysReset)

delay_cnt <= 32'd0;

else if(delay_cnt >= DELAY)

delay_cnt <= 32'd0;

else

delay_cnt <= delay_cnt + 1'b1;

end

reg [7:0] dig_show[9:0];

initial begin

dig_show[0] = 8'hC0;

dig_show[1] = 8'hF9;

dig_show[2] = 8'hA4;

dig_show[3] = 8'hB0;

dig_show[4] = 8'h99;

dig_show[5] = 8'h92;

dig_show[6] = 8'h82;

dig_show[7] = 8'hF8;

dig_show[8] = 8'h80;

dig_show[9] = 8'h90;

end

reg [7:0] dig_d = 8'b1111_1110;

reg [7:0] digCnt = 0;

always @(posedge sysClk)

begin

if(delay_cnt >= DELAY)

begin

dig_d <= {dig_d[6:0],dig_d[7]};

digCnt <= digCnt + 1;

if(digCnt == 8'd7)

digCnt <= 8'd0;

end

end

assign SEG = dig_show[digCnt];

assign DIG = dig_d;

assign led = dig_d;

endmodule

效果图:

动态数码管显示:

视频效果:

关键代码:

module aaa(

input sysClk,

input sysReset,

output [7:0] led,

output [7:0] SEG,

output [7:0] DIG

);

parameter DELAY = 10000;

reg [31:0] delay_cnt = 0;

always @(posedge sysClk,negedge sysReset)

begin

if(!sysReset)

delay_cnt <= 32'd0;

else if(delay_cnt >= DELAY)

delay_cnt <= 32'd0;

else

delay_cnt <= delay_cnt + 1'b1;

end

reg [7:0] dig_show[9:0];

initial begin

dig_show[0] = 8'hC0;

dig_show[1] = 8'hF9;

dig_show[2] = 8'hA4;

dig_show[3] = 8'hB0;

dig_show[4] = 8'h99;

dig_show[5] = 8'h92;

dig_show[6] = 8'h82;

dig_show[7] = 8'hF8;

dig_show[8] = 8'h80;

dig_show[9] = 8'h90;

end

wire [7:0] dig_out[9:0];

assign dig_out[5] = 8'hbf;

assign dig_out[2] = 8'hbf;

//---s

wire [3:0] s_h,s_l;

wire m_en;

time_s s(

.clk(sysClk),

.rstn(sysReset),

.s_h(s_h),

.s_l(s_l),

.m_en(m_en)

);

//---m

wire [3:0]m_h,m_l;

wire h_en;

time_m m(

.clk(sysClk),

.rstn(sysReset),

.en(m_en),

.m_h(m_h),

.m_l(m_l),

.h_en(h_en)

);

//---h

wire [3:0] h_h,h_l;

time_h time_h(

.clk(sysClk),

.rstn(sysReset),

.en(h_en),

.h_h(h_h),

.h_l(h_l)

);

//chioce data

assign dig_out[7] = dig_show[h_h];

assign dig_out[6] = dig_show[h_l];

assign dig_out[4] = dig_show[m_h];

assign dig_out[3] = dig_show[m_l];

assign dig_out[1] = dig_show[s_h];

assign dig_out[0] = dig_show[s_l];

reg [7:0] dig_d = 8'b1111_1110;

reg [7:0] digCnt = 0;

always @(posedge sysClk)

begin

if(delay_cnt >= DELAY)

begin

dig_d <= {dig_d[6:0],dig_d[7]};

digCnt <= digCnt + 1;

if(digCnt == 8'd7)

digCnt <= 8'd0;

end

end

assign SEG = dig_out[digCnt];

assign DIG = dig_d;

assign led = dig_d;

endmodule

秒模块

module time_s(

input clk,

input rstn,

output [3:0] s_h,

output [3:0] s_l,

output m_en

);

parameter DELAY = 50_000_000;

reg [31:0] delay_cnt = 0;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

delay_cnt <= 32'd0;

else if(delay_cnt >= DELAY)

delay_cnt <= 32'd0;

else

delay_cnt <= delay_cnt + 1'b1;

end

reg [3:0] s_h_d = 4,s_l_d = 5;

reg m_en_d = 0;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

begin

s_h_d <= 4'd4;

s_l_d <= 4'd3;

end

else if(delay_cnt >= DELAY)

begin

m_en_d <= 1'b0;

s_l_d <= s_l_d + 1'b1;

if(s_l_d == 4'd9)

begin

s_l_d <= 4'd0;

s_h_d <= s_h_d + 1'b1;

if(s_h_d == 4'd5)

begin

m_en_d <= 1'b1;

s_h_d <= 4'd0;

end

end

end

else

m_en_d <= 1'b0;

end

assign s_h = s_h_d;

assign s_l = s_l_d;

assign m_en = m_en_d;

endmodule

分模块:

module time_m(

input clk,

input rstn,

input en,

output [3:0] m_h,

output [3:0] m_l,

output h_en

);

reg [3:0] m_h_d = 2,m_l_d = 7;

reg h_en_d = 0;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

begin

m_h_d <= 4'd2;

m_l_d <= 4'd7;

end

else if(en)

begin

h_en_d <= 1'b0;

m_l_d <= m_l_d + 1'b1;

if(m_l_d == 4'd9)

begin

m_l_d <= 4'd0;

m_h_d <= m_h_d + 1'b1;

if(m_h_d == 4'd5)

begin

h_en_d <= 1'b1;

m_h_d <= 4'd0;

end

end

end

else

h_en_d <= 1'b0;

end

assign m_h = m_h_d;

assign m_l = m_l_d;

assign h_en = h_en_d;

endmodule

时模块:

module time_h(

input clk,

input rstn,

input en,

output [3:0] h_h,

output [3:0] h_l

);

reg [3:0] h_h_d = 2,h_l_d = 3;

always @(posedge clk,negedge rstn)

begin

if(!rstn)

begin

h_l_d <= 4'd3;

h_h_d <= 4'd2;

end

else if(en)

begin

h_l_d <= h_l_d + 1'b1;

if(h_l_d == 4'd9)

begin

h_l_d <= 4'd0;

h_h_d <= h_h_d + 1'b1;

end

else if((h_h_d == 4'd2) & (h_l_d == 4'd3))

begin

h_h_d <= 4'd0;

h_l_d <= 4'd0;

end

end

end

assign h_h = h_h_d;

assign h_l = h_l_d;

endmodule

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |