【问答】FPGA的启动过程

要解决这个问题首先要了解FPGA上电初始化过程,这里我们是以ALTERA的ArriaGX的AS模式来进行研究。

第一步控制POR时间

FPGA的AS配置主要分为三个过程:复位、配置和初始化过程。在配置之前,还有一个POR过程,即一上电FPGA经过一个POR后才开始整个配置流程。而POR的时间可以控制,通过控制PORSEL引脚控制POR的时间,当PORSEL接高时POR的时间大概是12ms,当PORSEL接低时POR的时间大概是100ms。

第二步控制配置、初始化时间

POR之后,FPGA进入正常的配置过程。下面来详细研究这个三个过程,看看那些地方用户可以进行控制。

首先,这复位过程是 在POR的时候就开始了,POR的时候nconfig和nstatus均为低电平,进入复位过程,POR结束后FPGA释放nconfig信号,nconfig信号被外部上拉电阻拉高,由此进入配置过程。

其次配置过程,FPGA产生DCLK时钟,在该时钟的同步下FPGA向配置芯片发送配置命令或者地址以及读取配置数据。而DCLK可以有两种速度,一种20Mhz,另一种40Mhz,且对应的配置方式分别叫AS和Fast AS。只有容量EPCS16及以上的配置芯片支持Fast AS。所以通过提高DCLK时钟速率从而达到减少配置时间的目的。

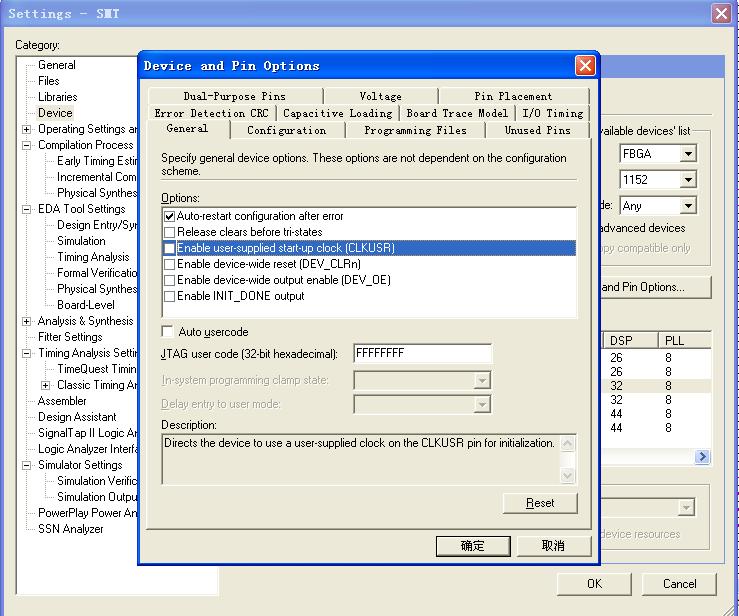

最后初始化过程,当所有的配置数据传输完毕以后,FPGA释放config_done信号,该pin被外部10K欧姆电阻上拉到高,FPGA是检测到CONFIG_DONE为高电平后进入到初始化过程。FPGA的初始化时钟源有两种选择,一种是FPGA内部产生DCLK的晶体分出的一个10Mhz的时钟,另一个是通过CLKUSR引脚控制可选时钟。默认情况下FPGA采用内部10Mhz时钟作为初始化时钟,如果要采用第二种时钟,则首先要做QII软件中使能Enable user-supplied start-up clock (CLKUSR) 选项(Settings->Device->Device and pin options...->General->本选项),如下图所示:

当上面可选项被使能以后CLKUSR引脚将作为FPGA初始化时钟源,用户可以在外部给该引脚提供一个时钟用来控制初始化时间。在这种情况下FPGA总共需要299个时钟周期完成初始化,CLKUSR支持最高时钟是100Mhz。Altera没有提供默认情况下初始化的时间(即官方没有提供默认情况下经过多少个10Mhz时钟周期完成初始化),所以一般使能CLKUSR是用来推迟FPGA退出初始化的时间,这里是研究能否通过CLKUSR来减少FPGA的初始化时间,这就必须要求我们获得Altera的官方的默认情况下FPGA的初始化时间。

下图是AS配置模式时序图:

关于上图中初始化时间即tcd2um在配置手册上有一个表里有最大和最小数据分别是100和20,但是该表没有单位,参考PS模式相应的参数,应该是us。也即默认情况下初始化时间最少也要20us,那么使能CLKUSR后初始化最小时间是多少呢?给出公式如下:

tCD2CU + (299 ×CLKUSR period)

上式中tCD2CU为从CONFIG_DONE变高到CLKUSR被使能的时间,手册上AS模式下给出的时间是100ns,所以上式最小值应该是100+299x10=3090ns,即不到4us。

上面讨论的是如何减少FPGA的配置、初始化时间,当然有些应用场合可能需要增加该时间,同样通过以上反过程可以达到目的。

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |

| 【分享开发笔记,赚取电动螺丝刀】墨水屏文本显示器被打赏¥25元 | |

| 【STEVAL-STWINKT1B】:结合STMcubeMX软件读取HTS221温湿度被打赏¥22元 | |

| M5PAPERESP32EINKDEVKIT评测|使用MicroPython开发M5Paper被打赏¥15元 | |

| OK1126B-S开发板下以导航按键控制云台/机械臂姿态调整被打赏¥29元 | |

| 【树莓派5】便携热成像仪被打赏¥36元 | |

| 【树莓派5】环境监测仪被打赏¥35元 | |

| OK1126B-S开发板下多时段语音提示型电子时钟被打赏¥27元 | |

| OK1126B-S开发板下函数构建及步进电机驱动控制被打赏¥25元 | |

| 【S32K3XX】LPI2C 参数配置说明被打赏¥20元 | |