全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。

根据全加器的功能,可列出它的真值表:

其中Ai和Bi分别是被加数及加数,Ci-1为相邻低位来的进位数,Si为本位和数(称为全加和)。以及Ci为向相邻高位的进位数。

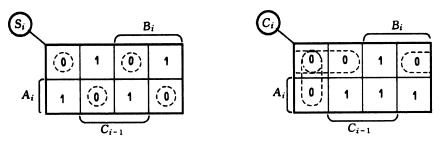

为了求出Si和Ci的逻辑表达式,首先分别画出Si和Ci的卡诺图:

为了比较方便地获得与-或-非的表达式,采用包围0的方法进行化简得:

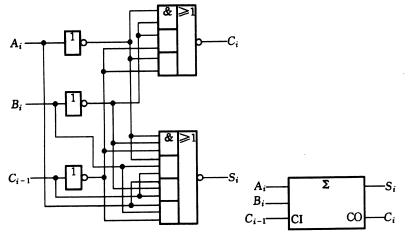

据此可以画出1位全加器的逻辑图:

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |

| 【分享开发笔记,赚取电动螺丝刀】墨水屏文本显示器被打赏¥25元 | |

| 【STEVAL-STWINKT1B】:结合STMcubeMX读取磁力计iis2mdc被打赏¥19元 | |

| 【STEVAL-STWINKT1B】:结合STMcubeMX读取LPS22HH气压、温度被打赏¥19元 | |

| 【STEVAL-STWINKT1B】:结合STMcubeMX读取STTS751温度被打赏¥17元 | |

| 【STEVAL-STWINKT1B】:结合STMcubeMX软件读取HTS221温湿度被打赏¥22元 | |

| M5PAPERESP32EINKDEVKIT评测|使用MicroPython开发M5Paper被打赏¥15元 | |

| OK1126B-S开发板下以导航按键控制云台/机械臂姿态调整被打赏¥29元 | |

| 【树莓派5】便携热成像仪被打赏¥36元 | |

| 【树莓派5】环境监测仪被打赏¥35元 | |