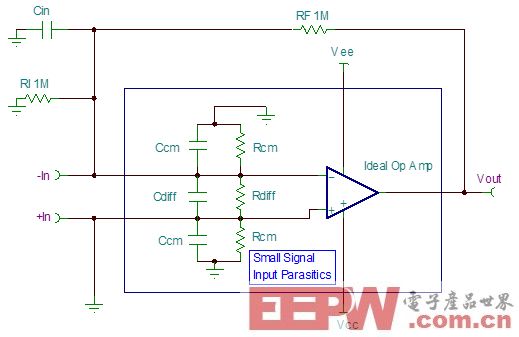

下图形象的说明了运放的输入端阻抗的特性。主要有两个参数,输入阻抗和输入电 容。对于电压反馈型运入,输入阻抗主要由输入级的决定,一般BJT输入级的运放。的共模输入阻抗会大于40MΩ。差模输入阻抗大于200GΩ。对于 JFET和CMOS输入级的运放,输入阻抗要大的多。这个阻抗通常表现为电阻性。作为常识被我们所熟知。

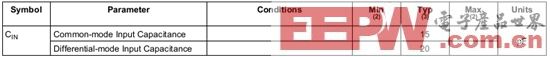

更值得我们多加关注的是运放的输入电容。这个参数通常在datasheet的表格中所列出,但常被忽视。运放的输入电容,通常分为共模输入电容Ccm和差模输入电容Cdiff。如下面是OPA376的datasheet中列出的输入电容。

对于有EMI抑制特性的运放,如LMV832,它的输入电容会被设计的正大的些。下面是带EMI抑制功能的LMV832的输入电容值。

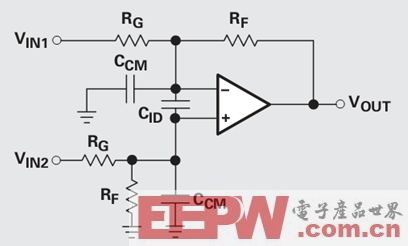

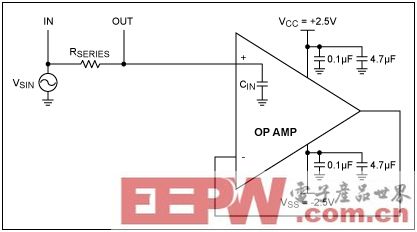

运放的输入共模电容Ccm 和差模电容 Cdiff会形成运放的输入电容 Cin。在许多应用中,运算放大器的输入电容都不会造成问题。但在某些应用中会引起放大电路的不稳定。尤其是反向输入端的电容,是放大电路不稳定的几大罪 魁祸首之一。如下图所示是运放在有输入电容的影响下的模型。

这个反向输入端的电容会在运放的环路增益中引入一个极点。正是这个极点的存在,在某些条件下,可能会引起放大电路的不稳定。

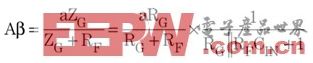

运放输入电容引入的极点如下式。即使这个极点0-dB交截越频率之内,而是非常靠近0-dB交越频率,它也有可能引起问题。在这个极点的频率点上,相位 会有45度的相位延迟,它很可能减少放大电路的相位裕度。如放大电路的0-dB交截越频率是2MHz。在2MHz处的相位裕度是89°。 如果这个极点的频率点也在2MHz处,它将使相位裕度减少45°。而变为φ = 89° – 45° = 44°。 44度的相位裕度就显得的不够了。

![]()

通常放大电路的输入电容不只由运放的输入电容组成,还包括布线引起的杂散电容和引脚电容。应尽量避免运算放大器反相输入端存在外部杂散电容,尤其是在高速 应用中。反相输入周围区域应去除接地层,从而最大程度地减小PC板杂散电容,此外,该引脚的所有连接都应尽量短。

在一些应用,常会加入反馈电容来增加放大电路的稳定,加入反馈电容后的电路的环路增益为,可见反馈补偿电容给环路增益中引入了一个零点。

关于运放电路稳定性,可以参阅Tim Green的系列文章。

Operational Amplifier Stability。

有一点需要引起注意,对于反向比例放大电路,如下图,它的同向端是接入到地的,由于“虚短”。此放运放的共模信号将为0,并且不随信号的变化而改变。因此共模信号引起的误差很小。

而对于同向比例放大电路,如下图,它的同向端是接的信号,由于“虚短”。此放运放的共模电压就是信号的电压。如果信号本身是一个频率很高的信号,幅值也很大。那么由这个信号引 入的Vos_CMRR_AC执必会非常大。此时应选用在信号频率上 CMRR依然很高的运放。经过上面的分析,即使这样,Vos_CMRR_AC的影响可能也会是非常严重的。“ 这是什么意思呢,没有明白,前面不是刚刚定义共模电压为两个输入端的平均值吗,怎么又和接地联系在一起了呢通常情况下我们可以在运放的datasheet中得到运放的输入电容Ccm和Cdif。这些值通常是典型值。有某些情况下,可能需要实测一下运放的输入电容,下面提供一种实用的测试方法。

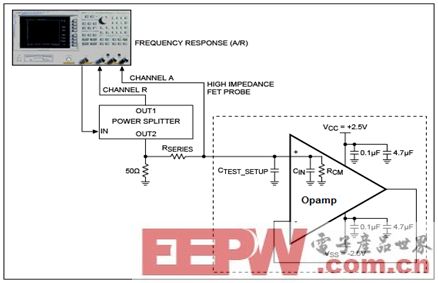

下图是测试的原理图,基本测试原理是把运放接成跟随器,然后在同向输入端串联一 个电阻(阻值一般在100K-1M之间),这个电阻与运放的输入电容会形成一个RC电路,我们测试出这个电路的-3dB频点,已知串联电阻。就可以计算出 运放的输入电容。这里需要注意的是,电阻也是有等效并联电容的。如一个典型的1/4W电容的等效并联电容约为0.3pF。我们可以通过串联电阻的方法来减 小电阻的等效并联电容。

下面的图片是实际测试的Setup。使用到的仪器有网络分析仪,高阻抗FET探头。和功耗分离器。为什么不用示波器呢?这是有原因的。

由于运放的输入电容通常是小于10pF的。示波器的探笔的电容通常是在10pF左右。如果用示波器探笔去测量运放的输入电容根本就无法测准。因此需要选用电容小于1pF的,高阻抗FET探头如Tektronix® P6245。

下面简要介绍一下测试方法:

(1)首先要测试未安装运放时PCB的杂散电容,网络分析仪的测试结果读出-3d频点f1。并计算出杂散电容:

(2)在电路中安装上运放,然后用网络分析仪测试出-3dB频点f2。并计算出运放输入电容与杂散电容的和:

(3)如果我们选取的串联电阻远小于运放的共模电阻,则可以看作Rth1=Rth2。则此时上式可以写为:

这样,求差,就可以计算出运放的输入电容了。

随着单电源运放的广泛的运用,运放的轨至轨输入(rail to rail input)成为一个时髦的词。现在大部分低电压单电源供电的运放都是轨至轨输入的。TI在轨至轨输入的运放产品方面具有十分领先的优势。本文介绍运放的 rail to rail输入的实现以及TI在实现运放的rail to rail 输入方面的领先技术。

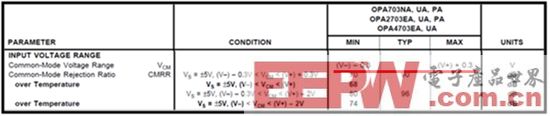

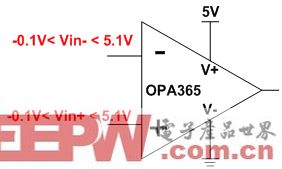

先说两句废话,解释一下轨至轨,这里的轨指的是电源轨,运放的两个电源供电电压如+/-15V。这两个电源电压就像两条平行的距离为30V的“轨道”一样 限制了运放的输入输出信号。运放的轨至轨输入是指运放的输入端信号电压能够达到电源的两个轨,并保持不失真,如上例输入信号电压可达到+/-15V。运放 的输入电压范围可在运放的datasheet中找到。就是共模电压范围Vcm(Common-Mode Voltage Range)。如下表即为OPA365的输入电压范围,可见它是典型的轨至轨输入运放。

![]()

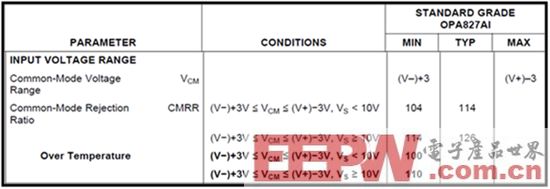

一般的BJT和JFET是非轨至轨输入的运放。如下表所示为OPA827共模输入电压范围为(V-)+3V至(V+)-3V,典型的非轨至轨运放。

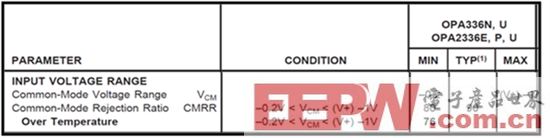

单电源(我们暂且称之为“单电源”)运放的输入级通常有三种结构,第一种是采用PMOS做差分输入级。这样的运入输入级电压可以低于负电源轨0.2甚至0.3V,但达不到正电源轨,如OPA336。下表是datasheet中标出的OPA336输入电压范围。

它的输入级原理框图如下图,典型的PMOS差分输入级。

既然PMOS差分输入级输入电压不能达到正电源轨,那NMOS呢,对头,NMOS差分输入级的输入电压可以达到正电源轨,但是达不到负电源轨,一般会在负电源轨的1.2V之上。

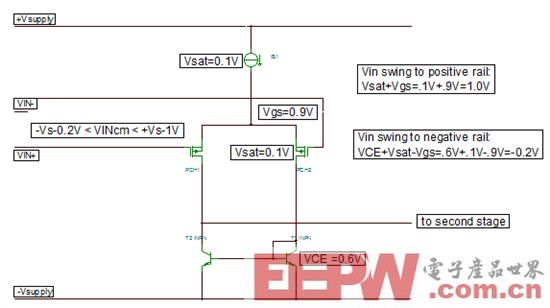

此时有人想到了,把PMOS和NMOS差分输入级并联起来。在接近电源负电压轨时使PMOS差分输入级工作,在接近电源正电源轨时使NMOS差分输入级 工作。这样不就可以实现运放的轨至轨输入了嘛。太巧妙了。的确早先的轨至轨输入运放就是这样设计的。并且现在也在大量使用这种技术。如下图是OPA703的输入级,就是典型的PMOS与NMOS相并联的运放输入级。当输入共模电压在(Vss-)-0.3V

下表是OPA703的datasheet中给出的共模电压输入范围(V-)-0.3V至(V+)+0.3V.

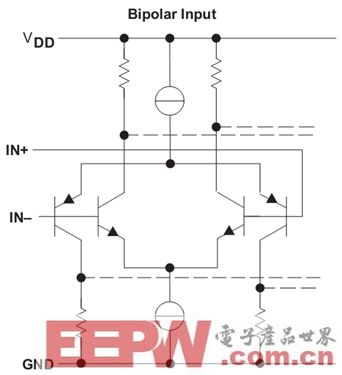

Bipolar输入级运入同样也有这样的结构,如下图是典型PNP与NPN型三级管并联形成的差分输入级。

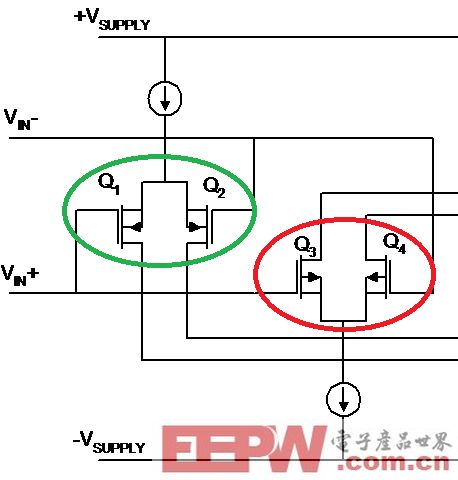

Part13中讲到了常用的轨至轨运放是采用NMOS与PMOS差分输入级相并联的方法。这一方法巧妙的解决了输入信号达不到两个电源轨的问题。在当今轨至轨输入的运放中得到广泛的应用。

但是这种并联差分输入级的运放有一个先天的问题就是输入失调电压交越问题。如下图所示,为并联差分输入结构的运放的输入前级。

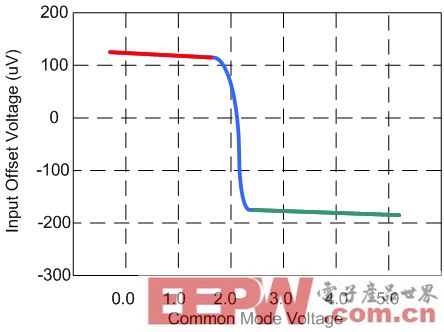

下图是这种运放的输入失调电压可以看出。随着共模电压的升高PMOS在2V(用于举例的值)左右将关闭,而NMOS即将打开,就在这个节骨眼上。运放的输入失调电压变生了跳变。这个可以理解,两组不同结构的输入级的输入失调电压是不同的,在交接棒时,这个失调电压也完成了交接棒。对于直流信号这个问题会 引起误差突变,对于正弦交流信号,这个问题会引起信号的失真。在交越点引入一个小小的台阶。

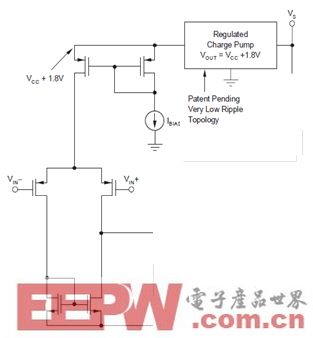

为了解决这个问题,TI公司设计了两种领先的差分输入级。第一种结构如下图。PMOS差分输入级能达到负电源轨,而达不到正电源轨,总是差这么1V左右够 不着。我们把输入级的电源在内部提高1.8V。水涨船高,这样的输入级就能达到运放的正电源轨。由于只有一组差分输入级,并不会存在输入失调电压交越的问 题。

这一技术在TI的单电源运放OPAl365上得到应用。如下图。

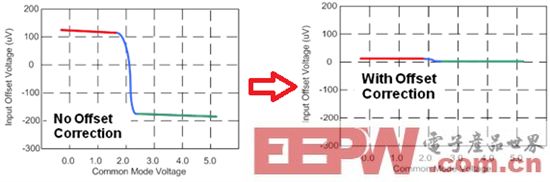

到这并没有结束,另一种技术在TI的单电源轨至轨运放中得到应用。这就是自调零技术。下图使用了自调零技术(MOSFET Zero Drift)前后。输入失调电压跳变就非常小了。

这一技术在TI的OPA333运放中得到应用,下表是OPA333的Vcm输入电压范围。

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |