源代码:

`timescale 1 ns/ 1 ps

module M4K_ram (clk,rst,data_out);

input clk,rst;

output[3:0] data_out;

reg[3:0] data_in;

reg[4:0] addr_cnt;

reg wren;

always @(posedge clk or negedge rst)

begin

if (!rst)

addr_cnt <= 0;

else

addr_cnt <= addr_cnt+1'b1;

end

always @(posedge clk or negedge rst)

begin

if (!rst)

wren <= 1'b1;

else if (addr_cnt == 5'd31)

wren <= ~wren;

end

always @(posedge clk or negedge rst)

begin

if (!rst)

data_in <= 0;

else if (addr_cnt == 5'd31 && ~wren)

data_in <= data_in + 1'b1;

end

ram ram_inst ( .address (addr_cnt),

.clock (clk),

.data (data_in),

.wren (wren),

.q (data_out) );

endmodule

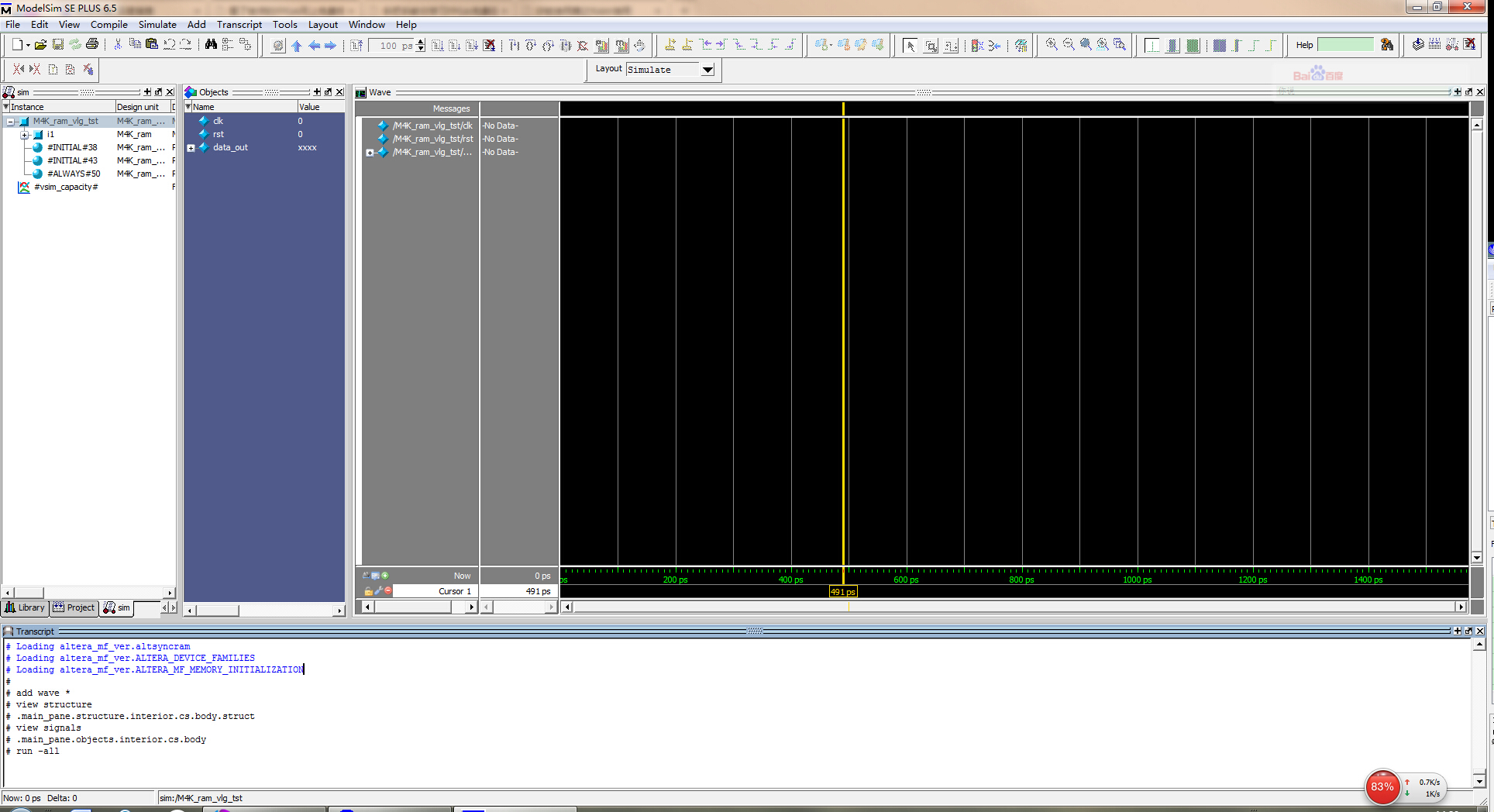

testbench为:

`timescale 1 ns/ 1 ps

module M4K_ram_vlg_tst();

reg clk;

reg rst;

wire [3:0] data_out;

M4K_ram i1 (

.clk(clk),

.data_out(data_out),

.rst(rst)

);

initial begin

clk=0;

forever

#10 clk= ~clk;

end

initial begin

rst=0;

#1000;

rst=1;

#20000;

$stop;

end

always

begin

end

endmodule

谢谢!

我要赚赏金

我要赚赏金