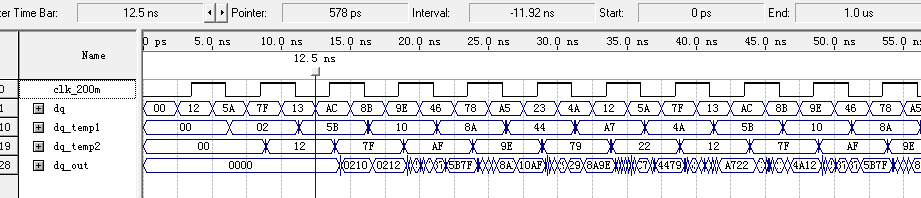

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY SampleFallingRising IS PORT(-------------clock signal----------------- clk_200m : IN std_logic; -------------input signal----------------- dq : IN std_logic_vector(7 DOWNTO 0); -------------output signal--------------- dq_out : OUT std_logic_vector(15 DOWNTO 0) ); END SampleFallingRising; ARCHITECTURE behave OF SampleFallingRising IS SIGNAL clk_200mn :std_logic; SIGNAL dq_temp1,dq_temp2 : std_logic_vector(7 DOWNTO 0); BEGIN clk_200mn<= NOT clk_200m; rising_sample :PROCESS(clk_200m) BEGIN IF(clk_200m'event AND clk_200m='1') THEN dq_temp1(7 DOWNTO 0)<=dq(7 DOWNTO 0); END IF; END PROCESS rising_sample; falling_sample :PROCESS(clk_200mn) BEGIN IF(clk_200mn'event AND clk_200mn='1') THEN -- dq_out(15 DOWNTO 8)<=dq_temp(7 DOWNTO 0); dq_temp2(7 DOWNTO 0)<=dq(7 DOWNTO 0); END IF; END PROCESS falling_sample; concatenation :PROCESS(clk_200m) BEGIN IF(clk_200m'event AND clk_200m='1') THEN dq_out<=dq_temp1&dq_temp2; END IF; END PROCESS concatenation; END behave;

我要赚赏金

我要赚赏金