前面发过I2S在左对齐模式下的输出逻辑波形,本次实验飞利浦模式下的输出。

在原来程序的基础上,只是简单修改工作模式,支出需要修改宏定义即可

//0: I2S 飞利浦标准

//1: MSB 左对齐标准

//2:LSB 右对齐标准

//3:PCM 标准

//#define STD_MODE 1 //I2S 标准选择

#define STD_MODE 0 // 飞利浦标准

//#define STD_MODE 2 // 右对齐标准

//#define STD_MODE 3 // PCM 标准

编译、下载、执行。

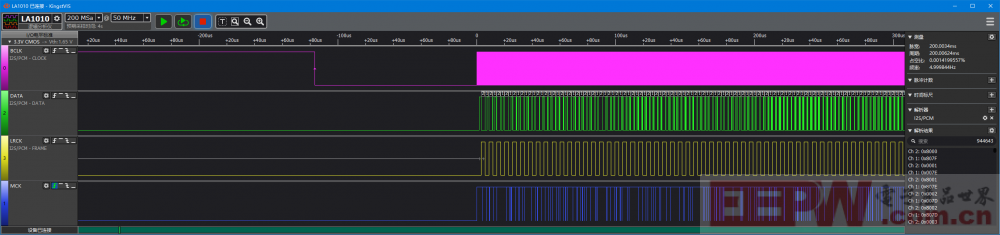

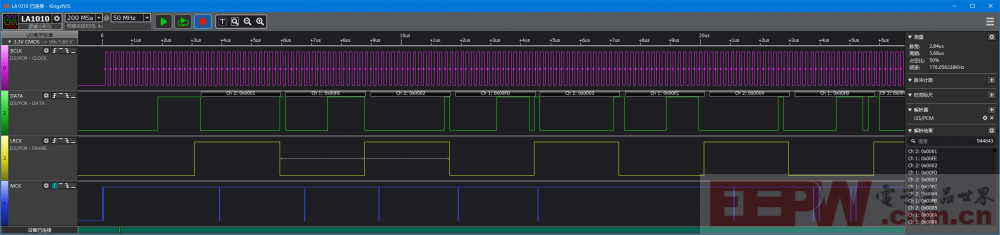

获得的逻辑波形:

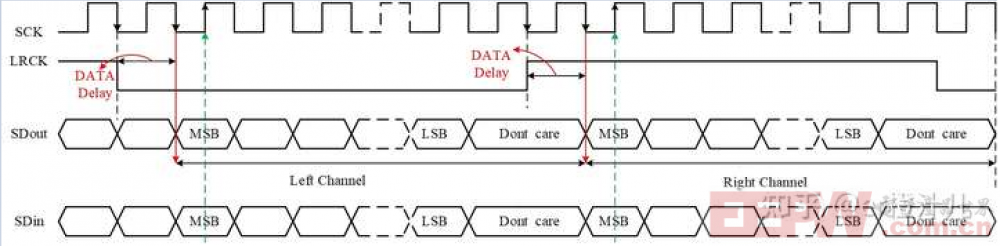

按照飞利浦标准的资料:

I2S格式的信号无论有多少位有效数据,数据的最高位总是被最先传输,它是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处。因此最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的 低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位(常补足为零)。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

对照看,感觉有以下是我无法理解的几个地方:

1、SCK的第一个信号发生时,LRCK信号没有高到低的变化

2、因为1的问题,程序中的0x00声道数据丢失

3、感觉LRCK信号提前了一个SCK周期那这一点非常明显。

但是,如果在忽视LRCK信号的话,在SCK的第二个时钟之后开始按照顺序处理SDA信号的话,除了第一个声道的数据0x00丢失外,其它数据按照时序处理,应该没有问题。

我要赚赏金

我要赚赏金