先推导一个结论:

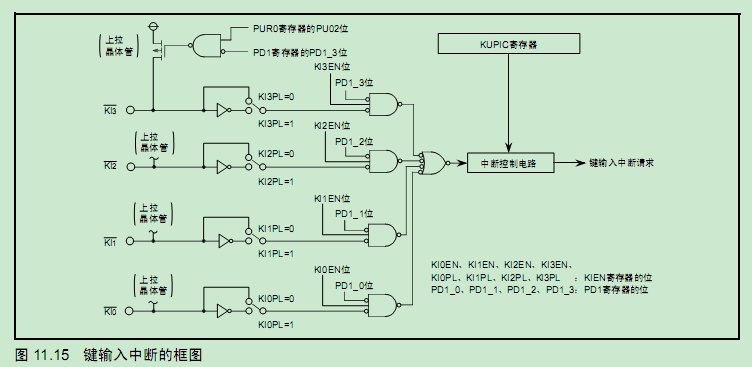

当PD1_i=0,(i=0,1,2,3),即设定为输入;

KI3EN=1,KI2EN=0,KI1EN=0;KI0EN=0;

KI3PL=1,即上升沿触发中断;

那么当KI3有一个上升沿时,“中断控制电路”之前也会给出一个下降沿,然后触发键盘中断,这样就得出结论:

如果“中断控制电路”之前给出一个下降沿,就应当会触发键盘中断。

现在假设:

在上述条件不变的情况下,给KI3一个上升沿(然后保持高电平),会触发键盘中断,

然后让KI3EN=0,则“中断控制电路”前恢复高电平,然后KI2EN=1,KI2PL=1,则如果KI2给出一个上升沿,“中断控制电路”前会产生一个下降沿,按理说这个下降沿应当也会触发键盘中断。也就是说,按照逻辑图分析,在给KI3一个上升沿并保持高电平后,只要KI3EN=0,KI2EN=1,KI2PL=1,则KI2的一个上升沿一样会触发键盘中断。

这就和手册的如下说明矛盾了:

我要赚赏金

我要赚赏金