首先谢谢板上的高手,

还想请教下,MIG产生的ucf文件里,IDELAYCTRL Location Constraints 怎么改呢

针对一个开发板我有IO和其他的位置分配,唯独缺这一项,在网上查了很久也没有结果哦

共9条

1/1 1 跳转至页

再请教一下,MIG的约束文件中IDELAYCTRL Location Constraints 怎么改呢

研究了几天问题基本解决了。

IDELAYCTRL 模块是为IDELAY模块服务的。DDR2中的u_iodelay_dq_ce用到了IDELAY模块,也就需要相应的IDELAYCTRL。但在改变约束文件里的IO loction时,它的位置约束要手动更改。

我是利用planahead来确定IDELAYCTRL的loction的。

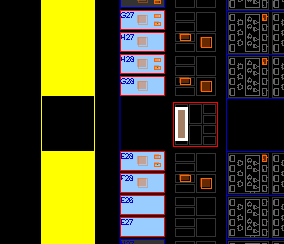

在device的视图中,找到约束文件中所定义的IDELAY的位置,就是下图橙色的方块。在它的附近找到IDELAYCTRL,图中白色的矩形,读出它的位置信息,再添到你的约束文件里就好了。DDR2总共要3个IDELAYCTRL。

希望这个对大家有帮助。

5楼

我以前做DDR2接口时,也是没有按IP CORE的引脚做的,但结果还是能用,也就没怎么改UCF文件,当然性能没有仔细去测试过。

9楼

楼主大人,我的ddr2数据引脚改动了,在ucf中约束到响应的iodelay上面,会连续出问题,有的说用mig更新,无论怎么该都会更新成默认状态,请大神指点一下怎么处理引脚改动这个问题。

共9条

1/1 1 跳转至页