wenyangzeng FPGA开发进程

1、购买器件,PCB板焊接

2、开发环境 QII9.0和谐:7楼

3、流水灯、跑马灯、闪烁灯

4、LED数码显示

5、字符型LCD显示

6、PS2键盘

7、按键控制LED

8、LED数码管显示DIP开关状态

9、串口通讯

10、DS1302数字时钟

11、交通灯

12、TLC549ADC

13、VGA彩条

14、音乐彩灯、警笛声、电子琴

15、DS18B20

16、可逆计数器

17、LCD数码时钟

18、I2C

19、数字频率计

wenyangzeng 进程贴 数字频率计

2楼

1. PCB板焊接

我申请的是方式二,购买PCB板和零件加USB Blaster下载器。收到包裹后开始焊接,焊接工具是30W外热式尖头电烙铁。这次的板比上次ARM DIY的PCB板布线和做工都好很多。但是核心板的过孔都没有阻焊,确实是一憾事,焊接过程很容易造成短路。比如C6电容焊盘附近就有2个过孔挨得很近,稍不注意就会出现短路。焊接后花了不少时间来检查焊盘和过孔间的短路,居然找出了3个短路点。PCB板加工成黑色确实漂亮,但是如果要查看布线情况却很费事。

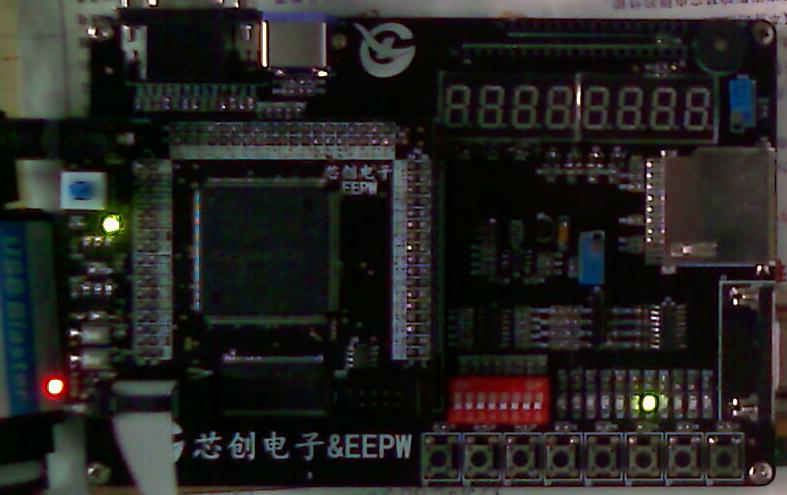

EP2C5Q208C8N暂时不焊接。先接通5V电源,测量3.3V和1.2V供电正常,最后才焊接该芯片,完成结果见图1(跑马灯已挂上)。

图1

我申请的是方式二,购买PCB板和零件加USB Blaster下载器。收到包裹后开始焊接,焊接工具是30W外热式尖头电烙铁。这次的板比上次ARM DIY的PCB板布线和做工都好很多。但是核心板的过孔都没有阻焊,确实是一憾事,焊接过程很容易造成短路。比如C6电容焊盘附近就有2个过孔挨得很近,稍不注意就会出现短路。焊接后花了不少时间来检查焊盘和过孔间的短路,居然找出了3个短路点。PCB板加工成黑色确实漂亮,但是如果要查看布线情况却很费事。

EP2C5Q208C8N暂时不焊接。先接通5V电源,测量3.3V和1.2V供电正常,最后才焊接该芯片,完成结果见图1(跑马灯已挂上)。

图1

3楼

2. 开发环境

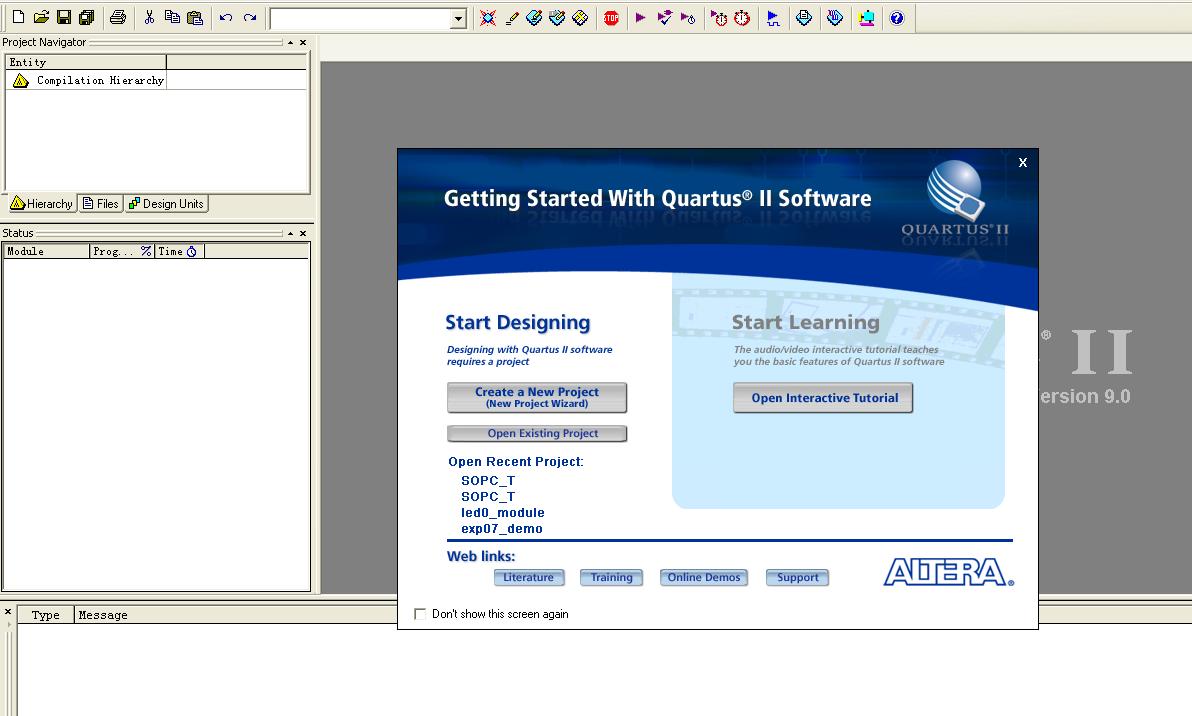

听说QuatusII 9.0以上使用不稳定,于是就安装9.0版的QuatusII 和NiosII 。

Quartus II 9.0

Nosii 9.0

USB Blaster

连接USB Blaster试下载.SOF文件到FPGA成功,开发准备工作就绪。

听说QuatusII 9.0以上使用不稳定,于是就安装9.0版的QuatusII 和NiosII 。

Quartus II 9.0

Nosii 9.0

USB Blaster

连接USB Blaster试下载.SOF文件到FPGA成功,开发准备工作就绪。

9楼

进程3:流水灯、跑马灯、闪烁灯

刚入门学习FPGA,遇到的困难主要是如何熟练使用Quaturesii软件工具生成最后的.SOF文件。经过几天刻苦练习,才稍稍学会软件工具的使用方法,就以跑马灯作为第一个进程,与各位共享生成.SOF的方法。

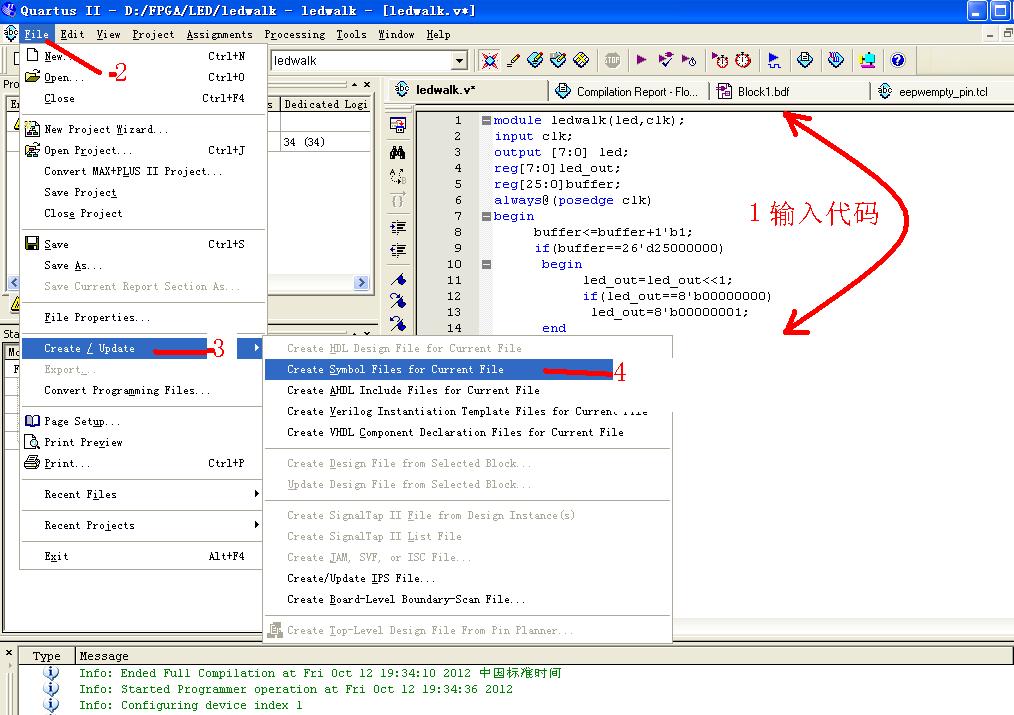

进入QUARTUSII9.0,建立一个新工程ledwalk; 点击File→NEW→Verilog HDL File,在文件编辑窗口中输入代码。 点击File→Create/Updata→Create Symbol Files for Current File见图1:1、2、3、4

图1

点击File→NEW→Block Diagram/Schematic file建立Block1.bdf;

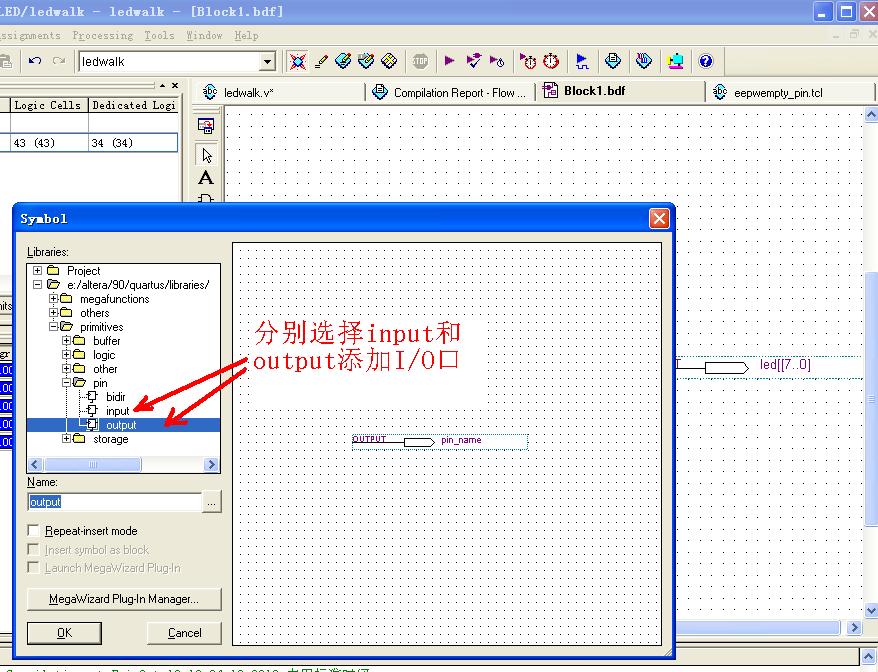

图2

双击Block1.bdf编辑窗口,见图2:1、2、3;

图3

出现图3 窗口,选择ledwalk,点击OK;

图4

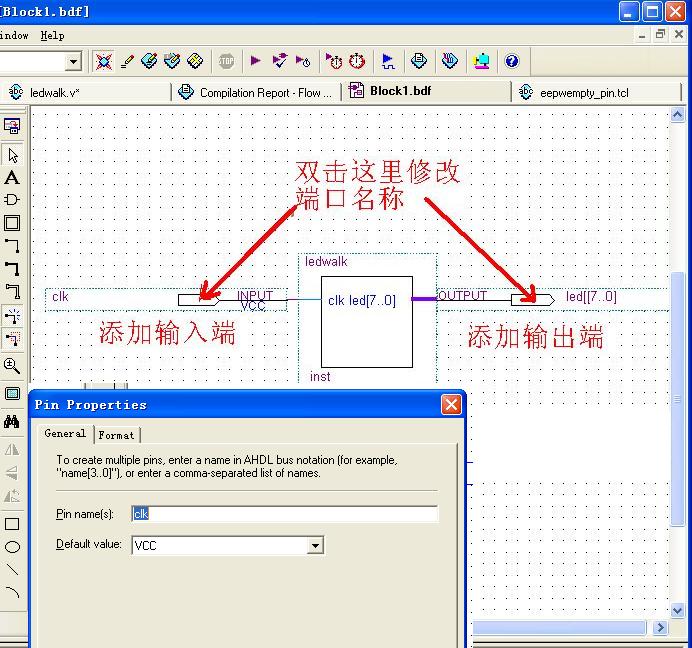

双击Block1.bdf编辑窗口,再分别添加输入和输出端口:图4

图5

连接好输入和输出端口到模块I/O口,分别双击图5中箭头所示之处,为端口修改名称clk和led[7..0]。

图6

点击:Tools →Tcl Scripts

选择eepwempty_pin.tcl文件(该文件必须预先存放在本项目文件夹)。点击Run(图6),消息窗口显示图6红线提示。

图7

点击:Start→Start Analysis & Synthesis执行一次确保无Error警告出现;

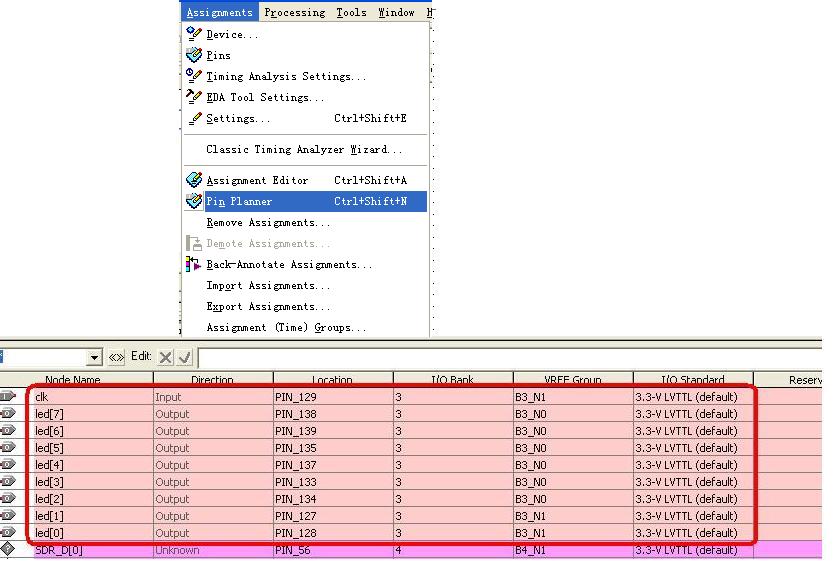

点击:Start→Start I/O Assigment Analysis执行管脚分配。图7

图8

点击Assignments→Pin Planner查看所分配的管脚的名称、方向、引脚编号已激活。见图8红色方框中。

点击Start compilation三角形箭头,进行最后编译生成ledwalk.sof就可以通过JTAG下载到FPGA片内了。

刚入门学习FPGA,遇到的困难主要是如何熟练使用Quaturesii软件工具生成最后的.SOF文件。经过几天刻苦练习,才稍稍学会软件工具的使用方法,就以跑马灯作为第一个进程,与各位共享生成.SOF的方法。

进入QUARTUSII9.0,建立一个新工程ledwalk; 点击File→NEW→Verilog HDL File,在文件编辑窗口中输入代码。 点击File→Create/Updata→Create Symbol Files for Current File见图1:1、2、3、4

图1

点击File→NEW→Block Diagram/Schematic file建立Block1.bdf;

图2

双击Block1.bdf编辑窗口,见图2:1、2、3;

图3

出现图3 窗口,选择ledwalk,点击OK;

图4

双击Block1.bdf编辑窗口,再分别添加输入和输出端口:图4

图5

连接好输入和输出端口到模块I/O口,分别双击图5中箭头所示之处,为端口修改名称clk和led[7..0]。

图6

点击:Tools →Tcl Scripts

选择eepwempty_pin.tcl文件(该文件必须预先存放在本项目文件夹)。点击Run(图6),消息窗口显示图6红线提示。

图7

点击:Start→Start Analysis & Synthesis执行一次确保无Error警告出现;

点击:Start→Start I/O Assigment Analysis执行管脚分配。图7

图8

点击Assignments→Pin Planner查看所分配的管脚的名称、方向、引脚编号已激活。见图8红色方框中。

点击Start compilation三角形箭头,进行最后编译生成ledwalk.sof就可以通过JTAG下载到FPGA片内了。

10楼

代码都是51FPAG提供的,谢谢大侠。

ledwalk.V:

module ledwalk(led,clk);

input clk;

output [7:0] led;

reg[7:0]led_out;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if(buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==8'b00000000)

led_out=8'b00000001;

end

end

assign led=led_out;

endmodule

//----------------------------

ledwater.V

module ledwater(clk,led);

output [7:0] led;

input clk;

reg[8:0] led_out;

reg[8:0] led_out1;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if (buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==9'b000000000)

led_out=9'b111111111;

led_out1=~led_out;

end

end

assign led=led_out1[7:0];

endmodule

//-------------------------------

led1.V

module led1 (clk ,led);

input clk;

output [7:0]led;

reg [7:0]led;

reg [25:0] buffer;

always@(posedge clk)

begin

buffer<=buffer+1;

if(buffer==26'd25000000)

begin

led<=~led;

buffer<=0;

end

end

endmodule

上一幅图就好了。

ledwalk.V:

module ledwalk(led,clk);

input clk;

output [7:0] led;

reg[7:0]led_out;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if(buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==8'b00000000)

led_out=8'b00000001;

end

end

assign led=led_out;

endmodule

//----------------------------

ledwater.V

module ledwater(clk,led);

output [7:0] led;

input clk;

reg[8:0] led_out;

reg[8:0] led_out1;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if (buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==9'b000000000)

led_out=9'b111111111;

led_out1=~led_out;

end

end

assign led=led_out1[7:0];

endmodule

//-------------------------------

led1.V

module led1 (clk ,led);

input clk;

output [7:0]led;

reg [7:0]led;

reg [25:0] buffer;

always@(posedge clk)

begin

buffer<=buffer+1;

if(buffer==26'd25000000)

begin

led<=~led;

buffer<=0;

end

end

endmodule

上一幅图就好了。

回复

| 有奖活动 | |

|---|---|

| 2026年“我要开发板活动”第三季,开始了! | |

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| PTC与NTC功能常规对比被打赏¥14元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于3pin锂电池接口的介绍/使用被打赏¥16元 | |

| 以启明云端ESP32P4开发板实现TF卡读写功能被打赏¥28元 | |

| 【分享开发笔记,赚取电动螺丝刀】树莓派5串口UART0配置被打赏¥25元 | |

| 【STM32F103ZET6】17:分享在Rtos项目中断管理的使用经验被打赏¥23元 | |

| 【STM32F103ZET6】16:分享在中断中恢复串口任务,遇到的问题被打赏¥31元 | |

| 在FireBeetle2ESP32-C5上实现温度大气压检测及显示被打赏¥21元 | |

| 【分享开发笔记,赚取电动螺丝刀】SAME51双串口收发配置被打赏¥27元 | |

| Chaos-nano操作系统在手持式VOC检测设备上的应用被打赏¥37元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于在导入第三方库lib时,wchart类型冲突的原因及解决方案被打赏¥30元 | |