从四层板到六层板再到八层板,一个不断优化和改进的过程。DDR走线设计是电子工程中的一个重要环节,对系统的性能和稳定性有着至关重要的影响。

在DDR走线设计中,选择合适的层数是一个关键的决策。四层板可能在一些简单的应用场景下足够使用,但随着对性能要求的提高,可能需要增加层数以优化走线布局和减少干扰。六层板和八层板提供了更多的布线空间和灵活性,有助于实现更高效的走线设计,并减少潜在的信号干扰和延时问题。

在您的设计过程中,可能还涉及到了其他方面的考虑,电源和地线的布局、信号线的长度和宽度、走线间的间距等。这些因素都会影响到DDR的性能和稳定性。通过不断的尝试和优化,您最终成功地使用了八层板完成了设计,这体现了您在电子工程领域的专业能力和实践经验。

此外,DDR走线设计还需要注意与其他电路板的兼容性以及生产过程中的工艺要求。确保设计符合相关标准和规范,并考虑到生产过程中的可行性和成本效益,也是非常重要的。

刚开始动作前查阅了蛮多的资料,最终我把找到的文档分享出来。

两片DDR走线规则主要包括以下几个方面:

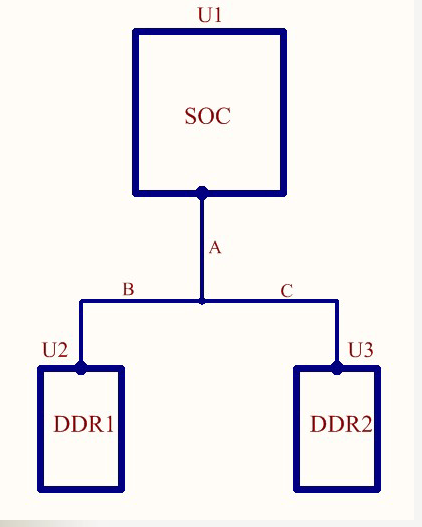

确定拓补结构:首先,需要确定DDR的拓补结构。DDR1/2一般采用星形结构,而DDR3则采用菊花链结构。星形拓补意味着地址线会走到两片DDR中间再分别向两片DDR走线,而菊花链则是用地址线将两片DDR“串”起来。

元器件摆放:在确定了DDR的拓补结构后,就可以进行元器件的摆放。摆放时应遵循以下原则:

考虑拓补结构,确保地址线有利于相应的拓补结构。

地址线上的匹配电阻应靠近CPU。

数据线上的匹配电阻应靠近DDR。

将DDR芯片摆放并旋转,使得DDR数据线尽量短,即DDR芯片的数据引脚靠近CPU。

如果有VTT端接电阻,应将其摆放在地址线可以走到的最远位置。通常,DDR2不需要VTT端接电阻,但DDR3则需要。

时钟线、地址线与命令控制线布线规则:

时钟线作为高速差分信号线,应按照差分布线规则进行布线,并在接收端进行阻抗匹配。

地址和命令信号线应进行端接匹配,通过匹配电阻接端接电源VTT。

数据线布线规则:

由于数据线采用了ODT技术,因此不需要外部进行端接匹配。

对于时钟线、地址线、命令控制线和数据线,等长布线要求较高。不仅每一组信号线内部要求等长布线,还要保持组间信号线尽量等长。

尽量保持同组信号线保持在同层,避免跨层布线。

为了避免信号间的串扰,对于差分信号线,应使用3W原则进行布线。

ROOM区域与规则:放置DDR和CPU的ROOM时,不需要很大,只需覆盖BGA焊盘即可。在走线时,可以利用小键盘的快捷键来扇出ROOM规则设置的过孔,并设置相应的规则以满足布线要求。

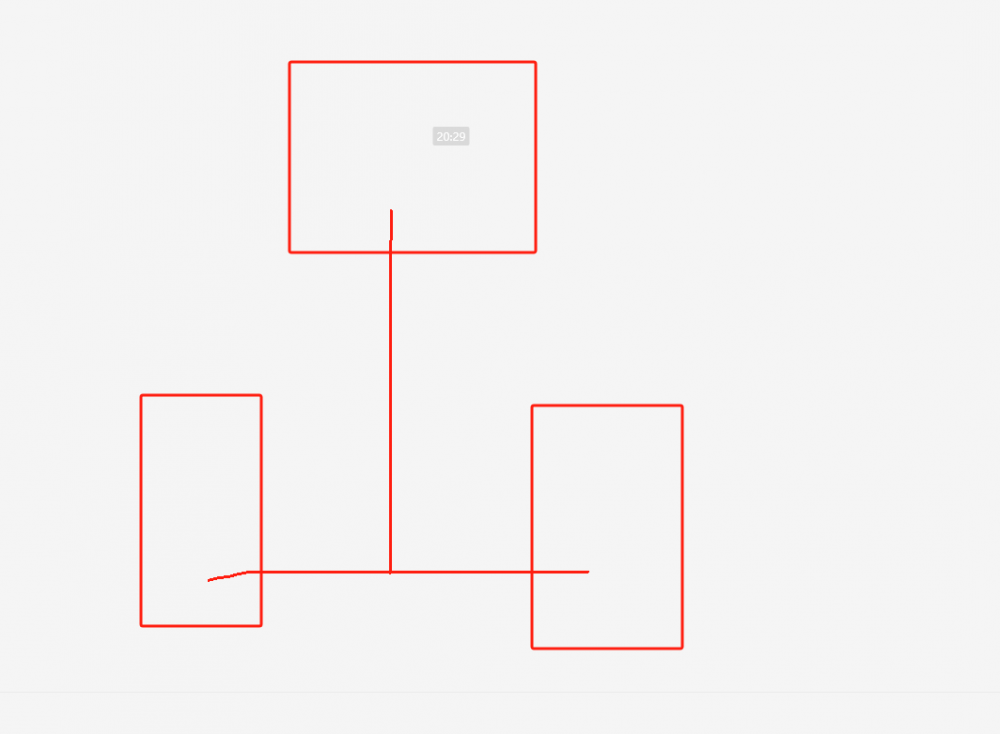

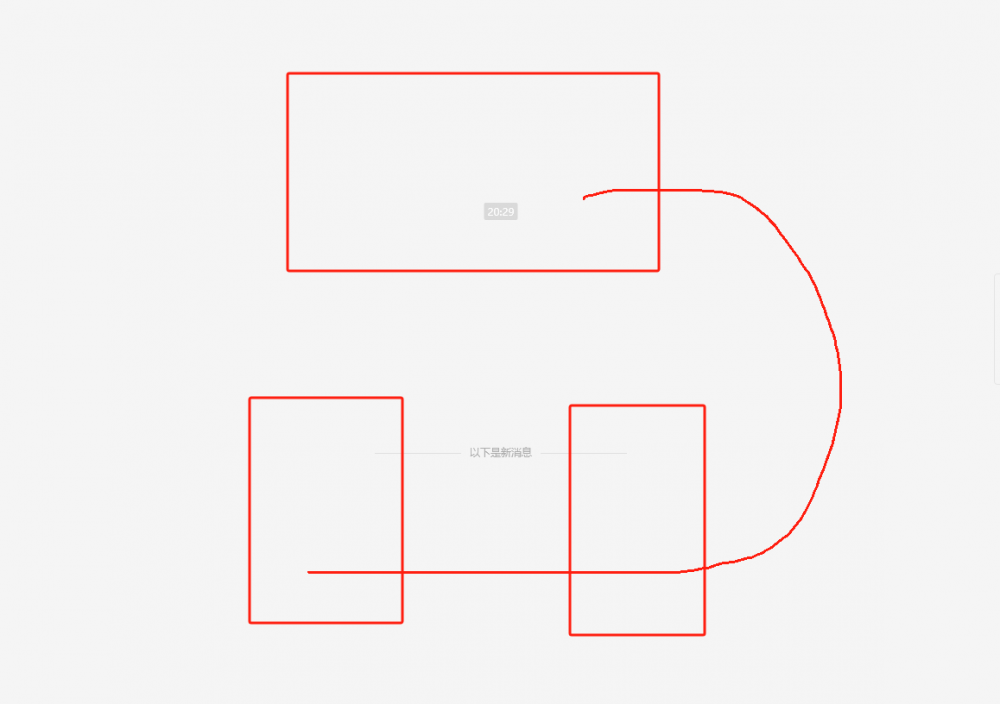

上面说了这么多,我总结一下,就是DDR要与FPGA足够近,然后要么走T型,要么走FLy by规则。这里我用简单的图表示一下,当时我的理解。

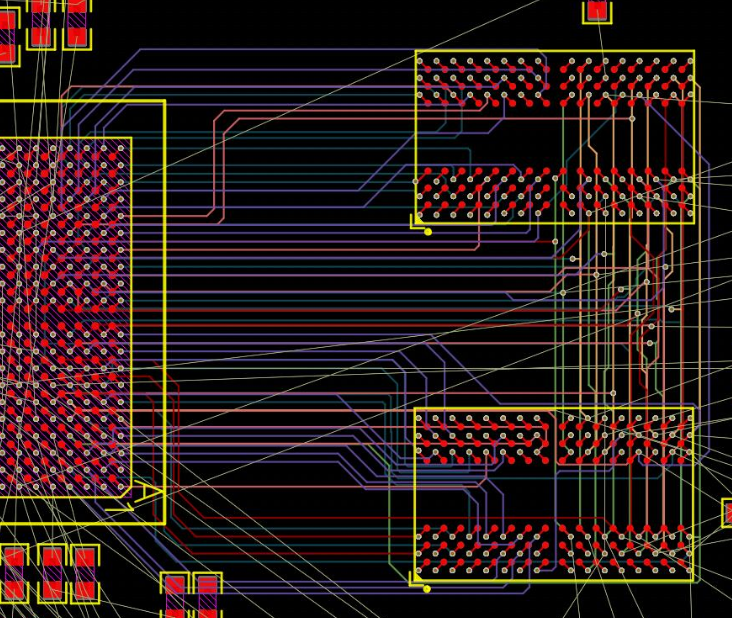

T型:

FLy by:

说到这里又要去找点资料解释一下:

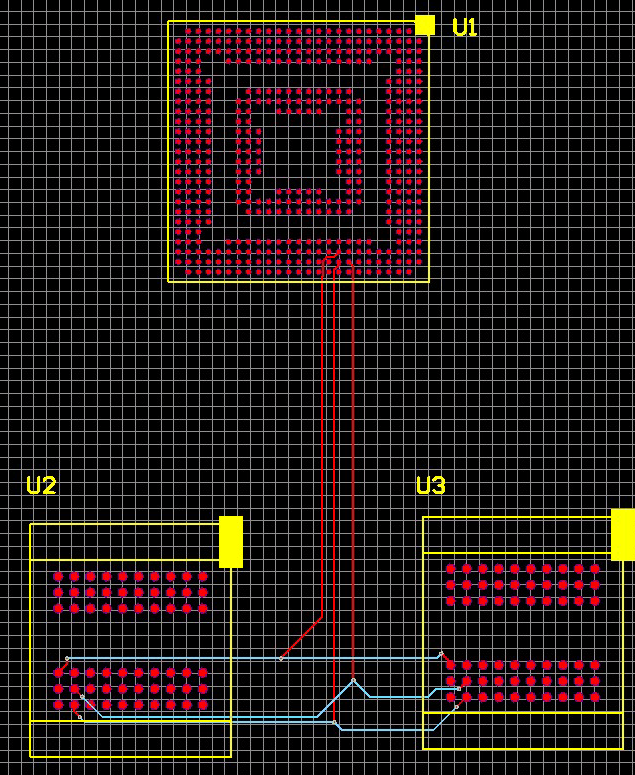

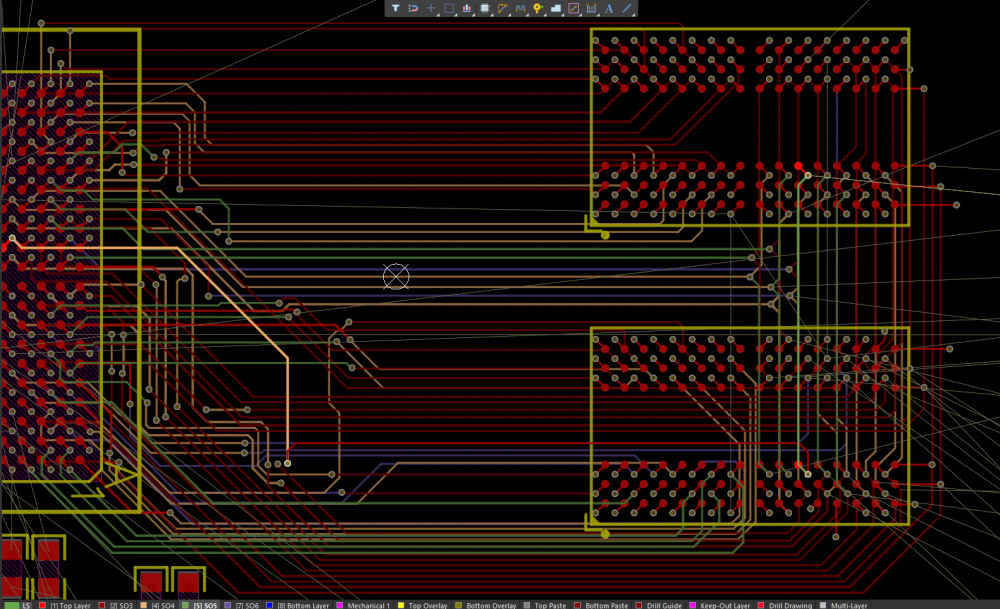

然后我走出来的效果与上图一样:

只能说几个,乱,真的好乱。

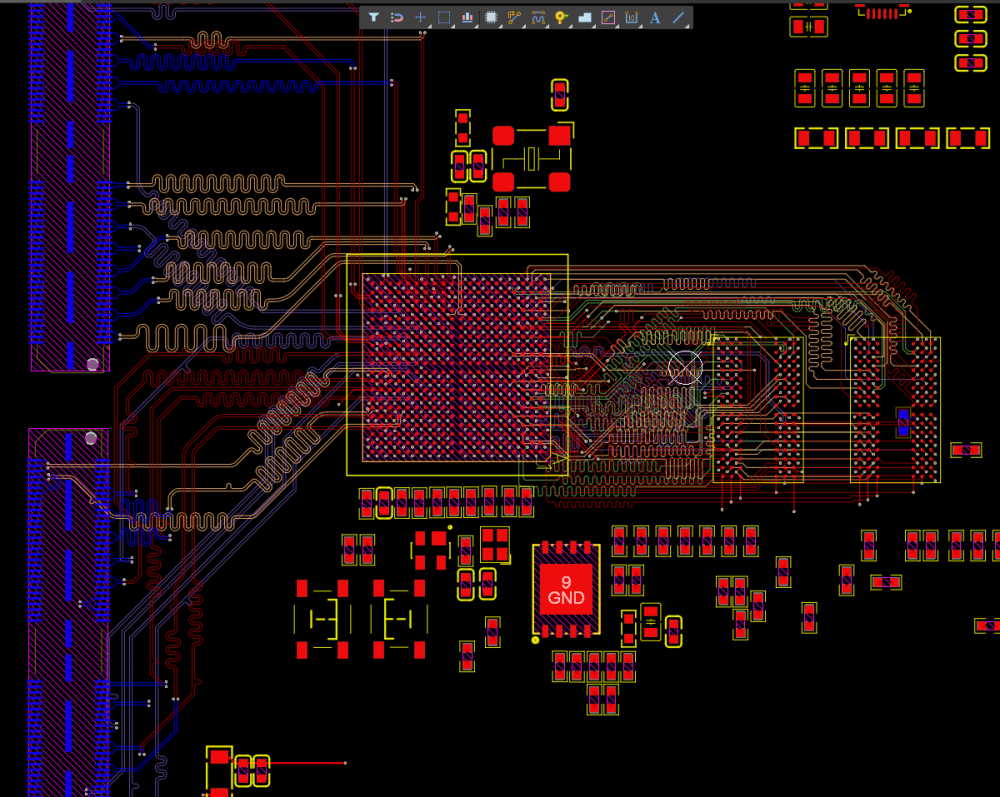

后面就用FLy by走了一篇,搞了两天,今天终于走通了。

自我感觉良好,论坛里的大神可以指点我一二。

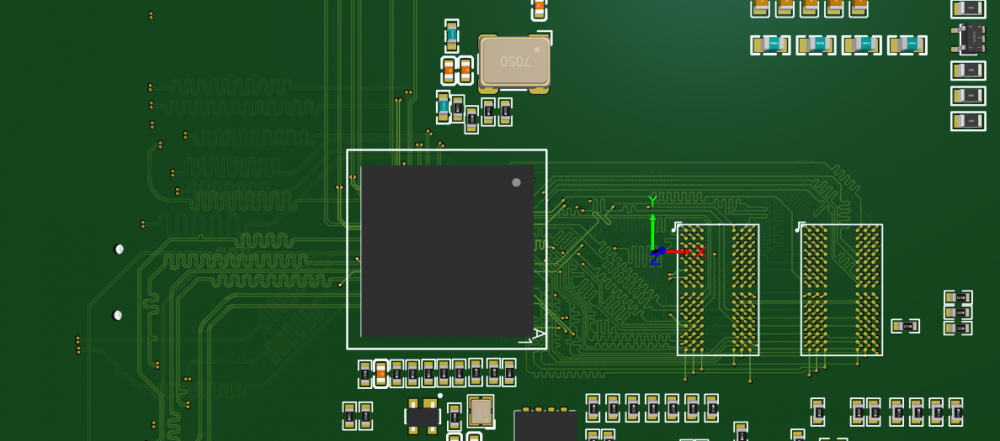

实际效果图:

要走线就需要对这几个方面的东西了解清楚,一个是过孔的大小,线的大小,以及间距,这个对走DDR 和FPGA差分非常的重要。

在布线过程中,过孔的大小、线的大小以及间距的设置对于DDR和FPGA差分走线至关重要。这些参数的选择不仅影响布线的难度和成本,还直接关系到电路的性能和可靠性。

首先,过孔是连接多层PCB中不同层走线的导体,对信号传输有着显著影响。在高频情况下,过孔的寄生电容和电感可能导致信号的反射、延时和衰减等问题。因此,在布线时需要仔细考虑过孔的大小。一般来说,过孔越小,其自身的寄生电容也越小,更适合用于高速电路。然而,过孔尺寸的减小会增加制造成本,并受到钻孔和电镀等工艺技术的限制。此外,过孔残桩的存在也可能降低过孔的阻抗值,引起谐振和损耗。因此,在确定过孔大小时需要权衡这些因素。

其次,线的大小,即线宽和线厚,对布线难度和电气性能也有显著影响。较粗的电线虽然能够降低电阻和提高载流能力,但会增加布线难度和成本。同时,线宽和线厚的选择也需要考虑与其他元件和过孔的匹配问题,以避免电气错误和漏电等问题。

最后,间距的设置同样重要。合理的走线间距不仅可以防止漏电和降低EMI(电磁干扰),还可以确保PCB的可靠性。间距过小可能导致带电导线间的短路,而间距过大则可能影响电气性能和EMC性能。因此,在设置间距时需要综合考虑这些因素,并根据具体的应用场景和需求进行调整。

我这边了解的供应商多层板最小要求过孔是0.15,0.25,线,0.075,间距是0.075,这个最小的极限了,再小就加工不出来的,听意思是这样讲的。

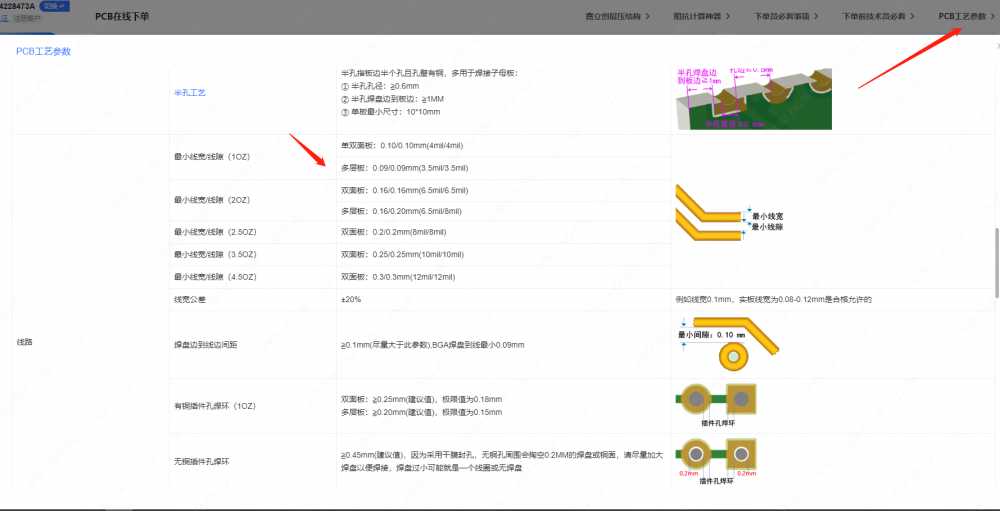

下面来看一下立创的:

线和间距:

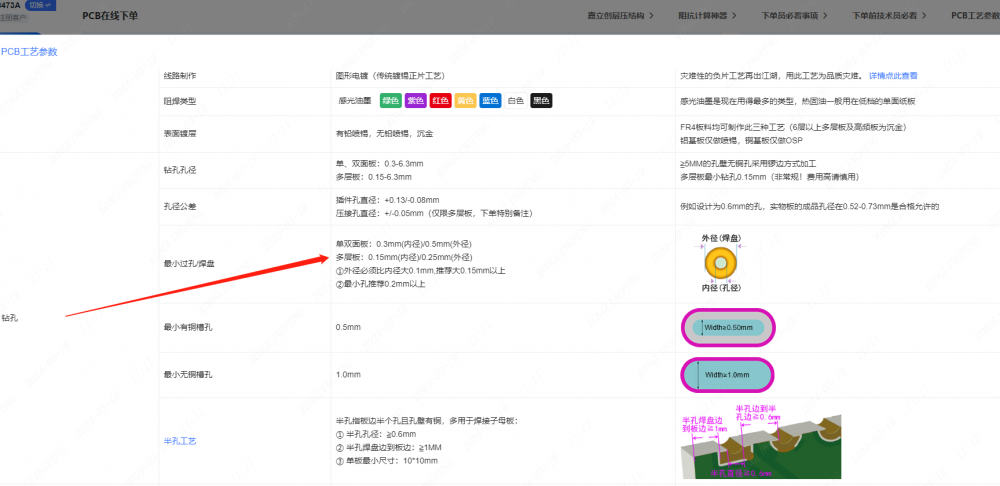

过孔:

过孔:

当然我这些给出来的是极限,能大一点的尽量要大一点,不要做的刚刚好,不然很难加工出来,而且这对PCB生产的要求也无形的加高了。