共7条

1/1 1 跳转至页

如何使用MIG3.6生成的example design

2楼

MIG3.6,这么高的版本啊,你用的ISE13.1吗?

我之前只用过MIG2.1的,我记得example design应该是可以直接仿真的。可以做一个状态机与DDR2 IP进行接口。

这个接口还是比较复杂的,建议你还是多花些时间看看DDR2 IP手册吧

我之前只用过MIG2.1的,我记得example design应该是可以直接仿真的。可以做一个状态机与DDR2 IP进行接口。

这个接口还是比较复杂的,建议你还是多花些时间看看DDR2 IP手册吧

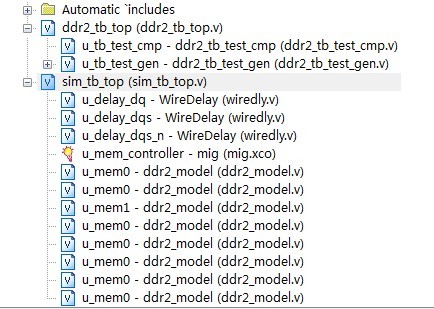

用的是ISE12.3的,里面自带的MIG。我用的是ISE自带的仿真器,把user design里面的仿真文件导入就能进行行为仿真,但导入example design里的仿真文件运行就会出这样的错:

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

user guide也看过了,里面就说把文件添加进去就行。。

你之前用的MIG2.1里面,example design和user design里面的东西有什么不同吗?

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

user guide也看过了,里面就说把文件添加进去就行。。

你之前用的MIG2.1里面,example design和user design里面的东西有什么不同吗?

7楼

哦。我用MIG3.4生成的,example design导入后顶层文件和testbench的端口不匹配。而用user design的就可以。

那你就在user design的基础上改吧

你的这个错误应该就是顶层文件找不到或接口不匹配的原因

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

那你就在user design的基础上改吧

你的这个错误应该就是顶层文件找不到或接口不匹配的原因

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

共7条

1/1 1 跳转至页

回复

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 在FireBeetle2ESP32-C5上实现温湿度检测和显示被打赏¥20元 | |

| 在FireBeetle2ESP32-C5上实现光照强度检测及显示被打赏¥21元 | |

| 以FireBeetle2ESP32-C5实现数据识读播报被打赏¥19元 | |

| 【STM32F103ZET6】14:实测STM32F1的串口输出任务的挂起与恢复功能被打赏¥27元 | |

| Chaos-nano在压力容器监控系统中的项目应用被打赏¥23元 | |

| 基于FireBeetle2ESP32-C5的WS2812B彩色灯带控制被打赏¥21元 | |

| SWM221CBT7显示开发板驱动TFT显示屏被打赏¥19元 | |

| SWM221CBT7显示开发板驱动OLED屏显示被打赏¥19元 | |

| SWM221CBT7显示开发板及其使用被打赏¥20元 | |

| 揭秘Chaos-nano:ArduinoProMini轻量级操作系统开发框架深度解析与实战应用被打赏¥19元 | |